9DBL0455 Overview

Description

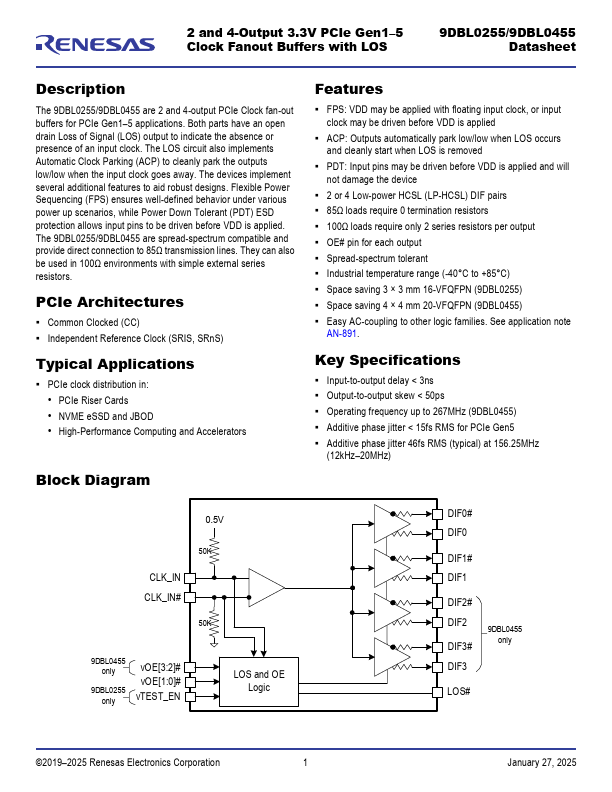

The 9DBL0255/9DBL0455 are 2 and 4-output PCIe Clock fan-out buffers for PCIe Gen1–5 applications. Both parts have an open drain Loss of Signal (LOS) output to indicate the absence or presence of an input clock.

Key Features

- See application note AN-891

- Key Specifications Input-to-output delay < 3ns Output-to-output skew < 50ps Operating frequency