9DML0451 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 24

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

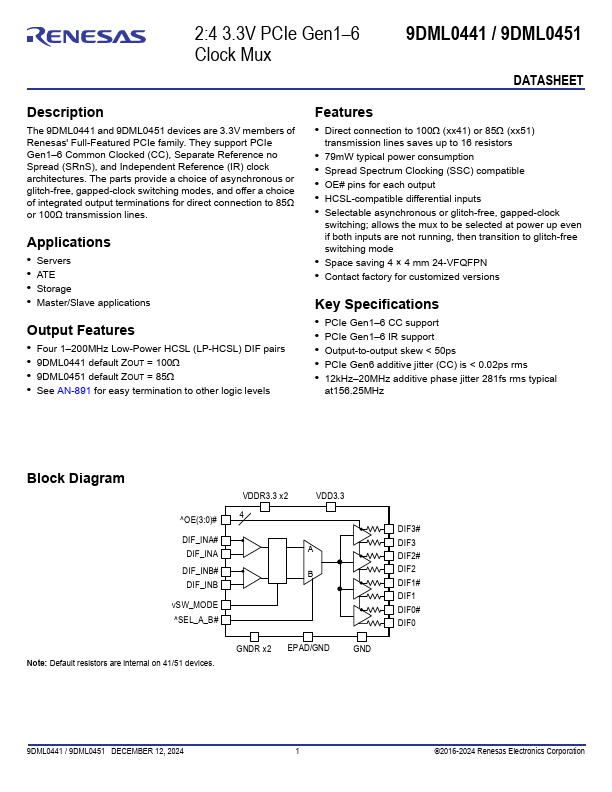

The 9DML0441 and 9DML0451 devices are 3.3V members of Renesas' Full-Featured PCIe family. They support PCIe Gen1–6 Common Clocked (CC), Separate Reference no Spread (SRnS), and Independent Reference (IR) clock architectures.

Key Features

- Direct connection to 100 (xx41) or 85 (xx51) transmission lines saves up to 16 resistors

- 79mW typical power consumption

- Spread Spectrum Clocking (SSC) compatible

- OE# pins for each output

- HCSL-compatible differential inputs

- Space saving 4 × 4 mm 24-VFQFPN

- Contact factory for customized versions Key Specifications

- PCIe Gen1–6 CC support

- PCIe Gen1–6 IR support

- Output-to-output skew < 50ps