CSPT855

FEATURES

:

- PLL clock driver for DDR (Double Data Rate) synchronous DRAM applications

- Spread spectrum clock patible

- Operating frequency: 60MHz to 220MHz

- Low jitter (cycle-to-cycle): ±50ps

- Distributes one differential clock input to four differential clock outputs

- Enters low power mode and 3-state outputs when input CLK signal is less than 20MHz or PWRDWN is low

- Operates from a 2.5V supply

- Consumes <200μA quiescent current

- External feedback pins (FBIN, FBIN) are used to synchronize outputs to input clocks

- Available in TSSOP package

APPLICATIONS:

- For all DDR1 speeds: PC1600 (DDR200), PC2100 (DDR266), PC2700 (DDR333), PC3200 (DDR400)

DESCRIPTION

:

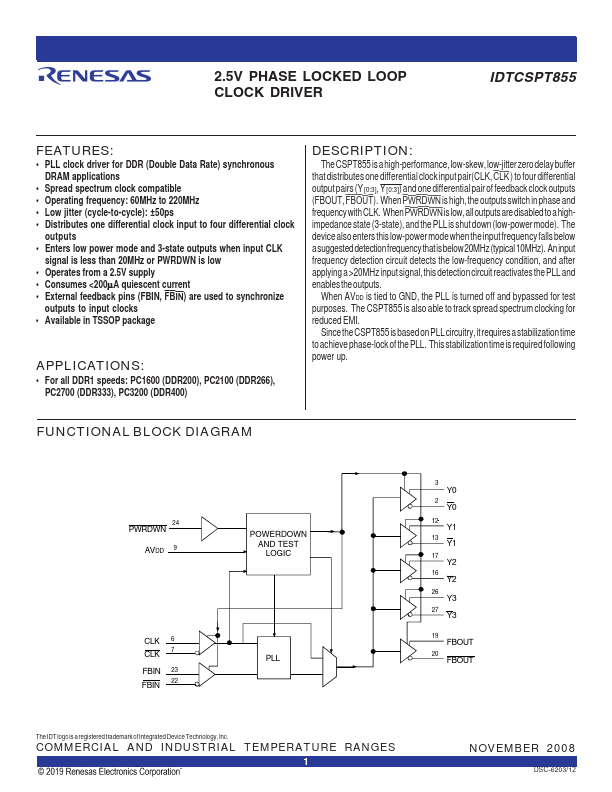

The CSPT855 is a high-performance, low-skew, low-jitter zero delay buffer that distributes one differential clock input pair(CLK, CLK ) to four differential output pairs (Y [0:3], Y [0:3]) and one differential pair of feedback clock outputs (FBOUT, FBOUT). When PWRDWN is high, the outputs switch in phase and frequency with...