EL4584

EL4584 is Horizontal Genlock manufactured by Renesas.

Features

- 36MHz, general purpose PLL

- 4FSC based timing (use the EL4585 for 8FSC)

- patible with EL4583 sync separator

- VCXO, Xtal, or LC tank oscillator

- < 2ns jitter (VCXO)

- User controlled PLL capture and lock

- patible with NTSC and PAL TV formats

- 8 pre-programmed TV scan rate clock divisors

- Selectable external divide for custom ratios

- Single 5V, low current operation

- Pb-Free available (Ro HS pliant)

Applications

- Pixel clock regeneration

- Video pression engine (MPEG) clock generator

- Video capture or digitization

- PIP (Picture-in-Picture) timing generator

- Text or graphics overlay timing

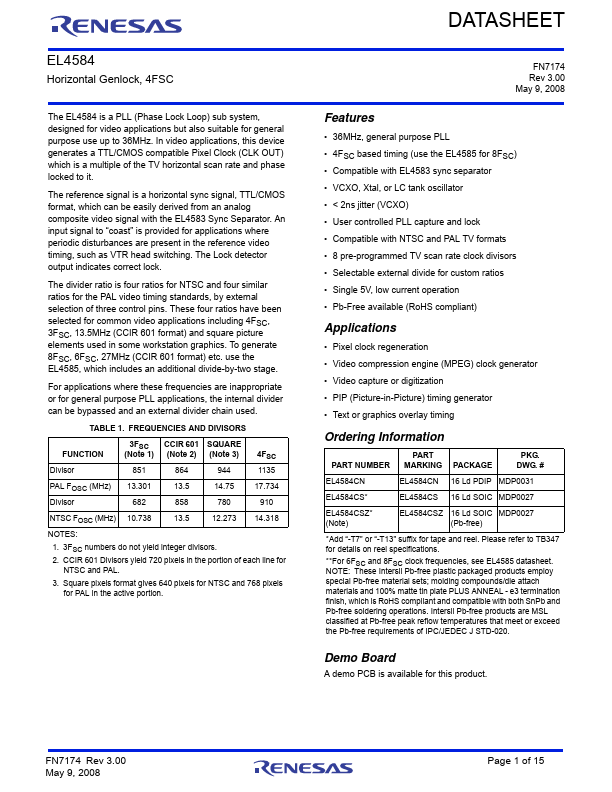

Ordering Information

PART PART NUMBER MARKING PACKAGE

PKG. DWG. #

EL4584CN

EL4584CN 16 Ld PDIP MDP0031

EL4584CS-

EL4584CS 16 Ld SOIC MDP0027

EL4584CSZ- (Note)

EL4584CSZ 16 Ld SOIC MDP0027 (Pb-free)

- Add “-T7” or “-T13” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- - For 6FSC and 8FSC clock frequencies, see EL4585 datasheet. NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding pounds/die attach materials and 100% matte tin...