HD74ACT112

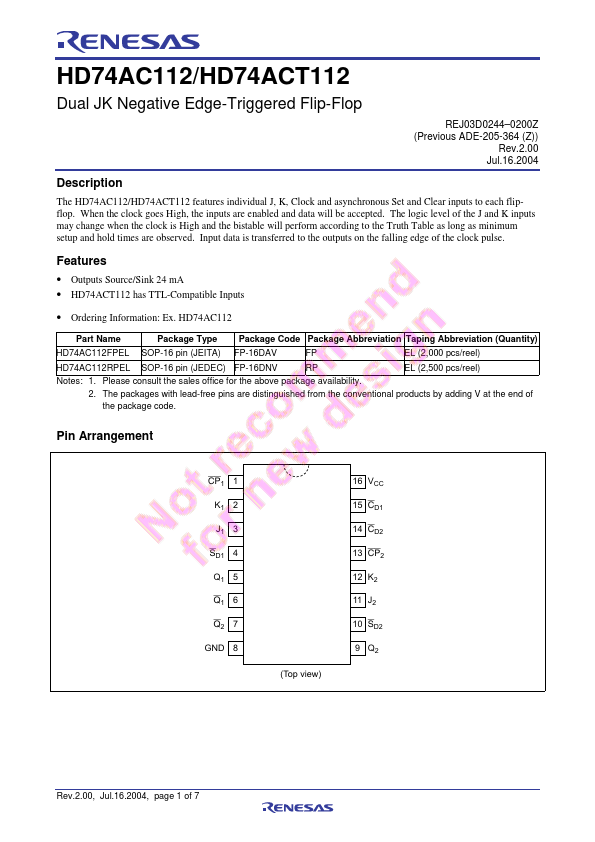

HD74ACT112 is Dual JK Negative Edge-Triggered Flip-Flop manufactured by Renesas.

- Part of the HD74AC112 comparator family.

- Part of the HD74AC112 comparator family.

Description

The HD74AC112/HD74ACT112 features individual J, K, Clock and asynchronous Set and Clear inputs to each flipflop. When the clock goes High, the inputs are enabled and data will be accepted. The logic level of the J and K inputs may change when the clock is High and the bistable will perform according to the Truth Table as long as minimum setup and hold times are observed. Input data is transferred to the outputs on the falling edge of the clock pulse.

Features

- Outputs Source/Sink 24 m A

- HD74ACT112 has TTL-patible Inputs

- Ordering Information: Ex. HD74AC112

Part Name

Package Type Package Code Package Abbreviation Taping Abbreviation (Quantity)

HD74AC112FPEL SOP-16 pin (JEITA) FP-16DAV

EL (2,000 pcs/reel)

HD74AC112RPEL SOP-16 pin (JEDEC) FP-16DNV

EL (2,500 pcs/reel)

Notes: 1. Please consult the sales office for the...