HD74CDCV857A

HD74CDCV857A is 2.5-V Phase-lock Loop Clock Driver manufactured by Renesas.

2.5-V Phase-lock Loop Clock Driver

REJ03D0136- 0300Z (Previous ADE-205-693B (Z))

Rev.3.00 Oct.09.2003

Description

The HD74CDCV857A is a high-performance, low-skew, low-jitter, phase locked loop clock driver. It is specifically designed for use with DDR (Double Data Rate) synchronous DRAMs.

Features

- DDR333 / PC2700-pliant, also meets DDR266 / PC2100 requirement.

- Supports 60 MHz to 170 MHz operation range

- Distributes one differential clock input pair to ten differential clock outputs pairs

- Supports spread spectrum clock requirements meeting the PC100 SDRAM registered DIMM specification

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input

- Supports 2.5V analog supply voltage (AVCC), and 2.5 V VDDQ

- No external RC network required

- Sleep mode detection

- 48pin TSSOP (Thin Shrink Small Outline Package)

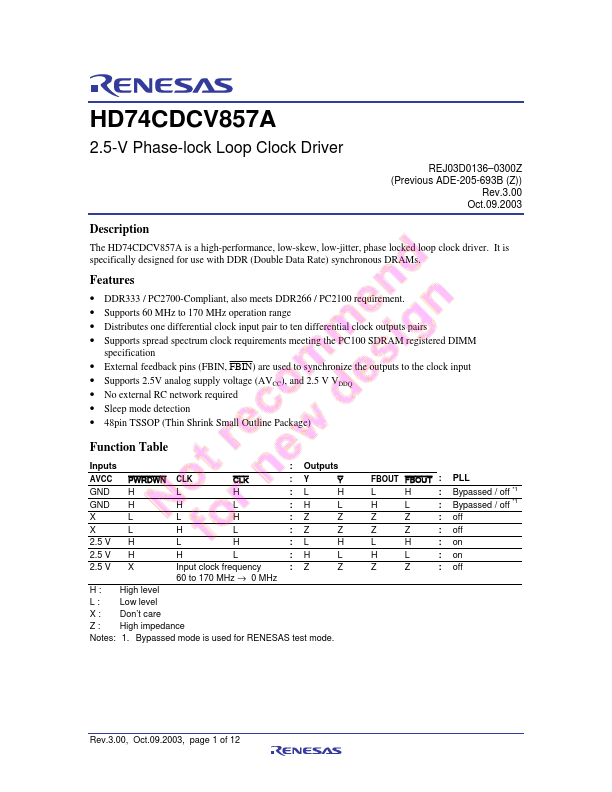

Function Table

Inputs

: Outputs

AVCC PWRDWN CLK

:Y

GND H

:L

GND...