HD74HC78

HD74HC78 is Dual J-K Flip-Flops manufactured by Renesas.

Description

This flip-flop is edge sensitive to the clock input and change state on the negative transition of the clock pulse. Each flip-flop has independent J, K, and preset inputs and Q and Q outputs. Two flip-flops are controlled by a mon clear and a mon clock. Preset and clear are independent of the clock and acplished by a low logic level on the corresponding input.

Features

- High Speed Operation: tpd (Clock to Q) = 20 ns typ (CL = 50 p F)

- High Output Current: Fanout of 10 LSTTL Loads

- Wide Operating Voltage: VCC = 2 to 6 V

- Low Input Current: 1 µA max

- Low Quiescent Supply Current: ICC (static) = 2 µA max (Ta = 25°C)

- Ordering Information

Part Name

Package Type

Package Code (Previous Code)

Package Abbreviation

HD74HC78FPEL SOP-14 pin (JEITA)

PRSP0014DF-B (FP-14DAV)

HD74HC78RPEL SOP-14 pin (JEDEC)

PRSP0014DE-A (FP-14DNV)

Note: Please consult the sales office for the above package availability.

Taping Abbreviation (Quantity)

EL (2,000 pcs/reel)

EL (2,500 pcs/reel)

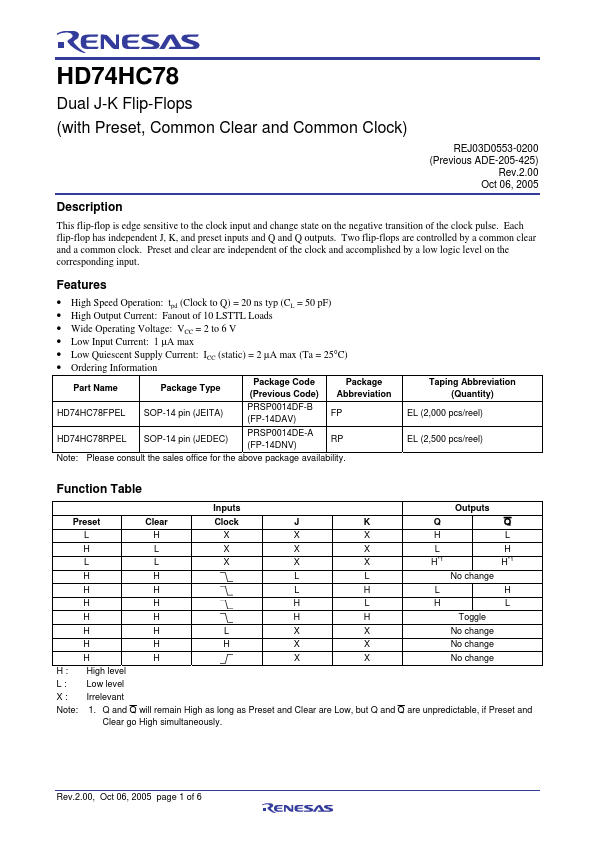

Function Table

Inputs

Outputs

Preset

Clear

Clock

LHX XXH L

HLXXXLH L L X X X H- 1 H- 1

No...