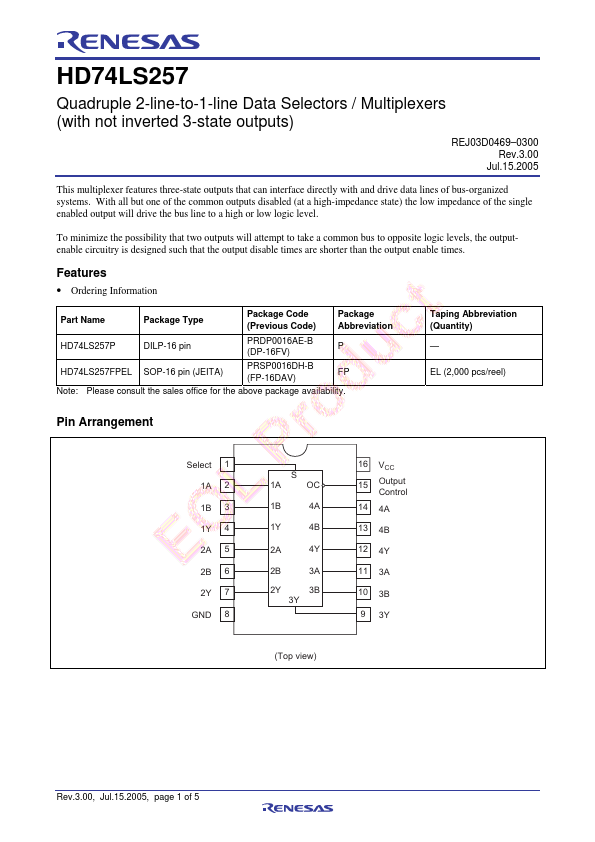

| Part | HD74LS257P |

|---|---|

| Description | Quadruple 2-line-to-1-line Data Selectors/Multiplexers |

| Manufacturer | Renesas |

| Size | 167.17 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HD74LS257 | Hitachi Semiconductor | Quadruple 2-line-to-1-line Data Selectors/Multiplexers |

| HD74LS258 | Hitachi Semiconductor | Quadruple 2-line-to-1-line Data Selectors/Multiplexers |

| HD74LS251 | Hitachi Semiconductor | 1 of 8 Data Selectors/Multiplexers |

| HD74LS259 | Hitachi Semiconductor | 8-bit Addressable Latches |

| HD74LS253 | Hitachi Semiconductor | Dual 4-line-to-1-line Data Selectors/Multiplexers |