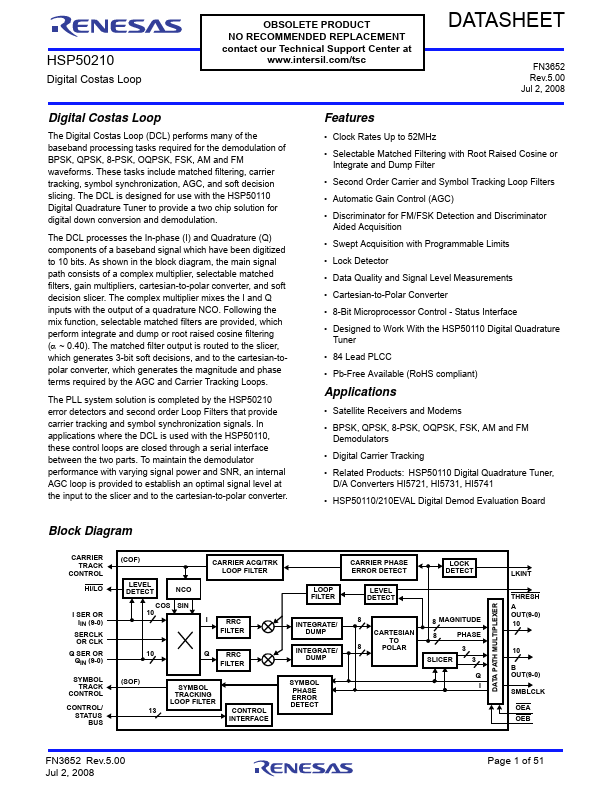

HSP50210

Key Features

- Clock Rates Up to 52MHz

- Selectable Matched Filtering with Root Raised Cosine or Integrate and Dump Filter

- Second Order Carrier and Symbol Tracking Loop Filters

- Automatic Gain Control (AGC)

- Discriminator for FM/FSK Detection and Discriminator Aided Acquisition

- Swept Acquisition with Programmable Limits

- Lock Detector

- Data Quality and Signal Level Measurements

- Cartesian-to-Polar Converter

- 8-Bit Microprocessor Control - Status Interface