ICS548A-03

Overview

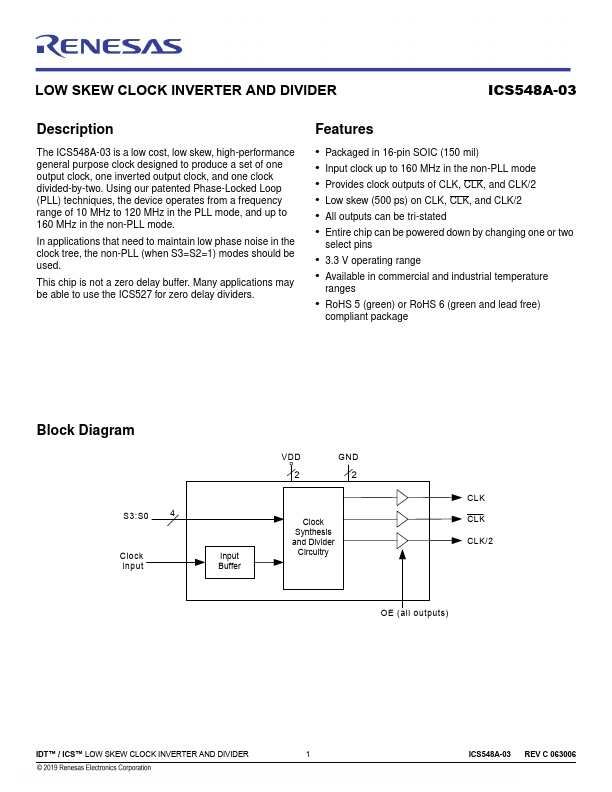

The ICS548A-03 is a low cost, low skew, high-performance general purpose clock designed to produce a set of one output clock, one inverted output clock, and one clock divided-by-two. Using our patented Phase-Locked Loop (PLL) techniques, the device operates from a frequency range of 10 MHz to 120 MHz in the PLL mode, and up to 160 MHz in the non-PLL mode.

- Packaged in 16-pin SOIC (150 mil)

- Input clock up to 160 MHz in the non-PLL mode

- Provides clock outputs of CLK, CLK, and CLK/2

- Low skew (500 ps) on CLK, CLK, and CLK/2

- All outputs can be tri-stated

- Entire chip can be powered down by changing one or two select pins

- 3.3 V operating range

- Available in commercial and industrial temperature ranges

- RoHS 5 (green) or RoHS 6 (green and lead free) compliant package