ICS621 Overview

Description

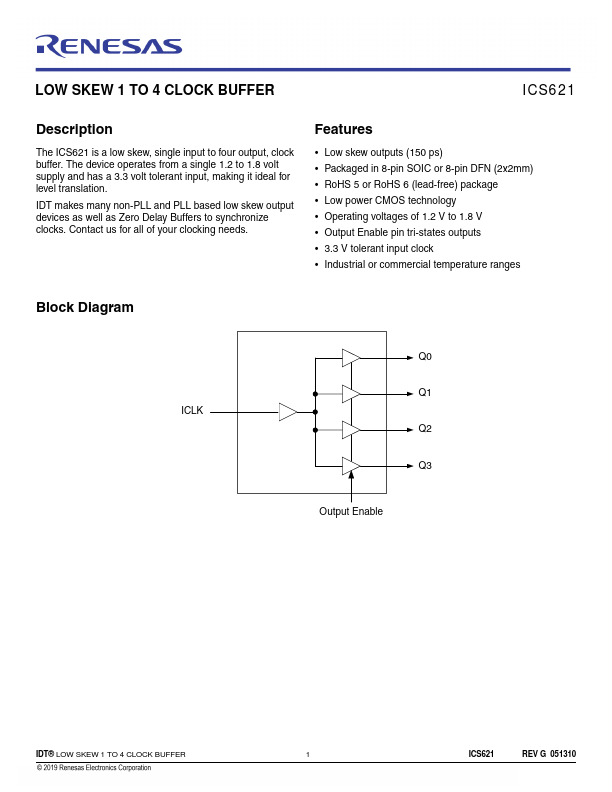

The ICS621 is a low skew, single input to four output, clock buffer. The device operates from a single 1.2 to 1.8 volt supply and has a 3.3 volt tolerant input, making it ideal for level translation.

Key Features

- Low skew outputs (150 ps)

- Packaged in 8-pin SOIC or 8-pin DFN (2x2mm)

- RoHS 5 or RoHS 6 (lead-free) package

- Low power CMOS technology

- Operating voltages of 1.2 V to 1.8 V

- Output Enable pin tri-states outputs

- 3.3 V tolerant input clock

- Industrial or commercial temperature ranges