ICS8543

ICS8543 is Differential-to-LVDS Fanout Buffer manufactured by Renesas.

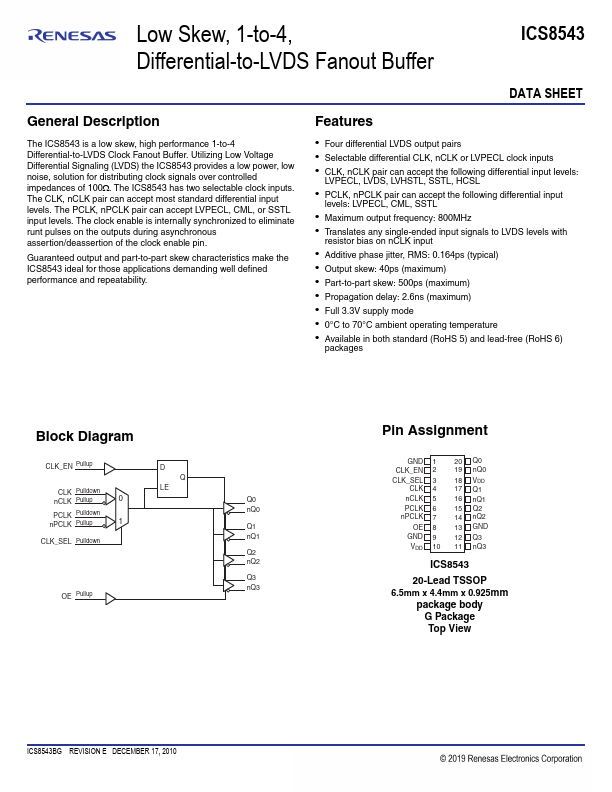

Low Skew, 1-to-4, Differential-to-LVDS Fanout Buffer

General Description

The ICS8543 is a low skew, high performance 1-to-4 Differential-to-LVDS Clock Fanout Buffer. Utilizing Low Voltage Differential Signaling (LVDS) the ICS8543 provides a low power, low noise, solution for distributing clock signals over controlled impedances of 100Ω. The ICS8543 has two selectable clock inputs. The CLK, nCLK pair can accept most standard differential input levels. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin.

Guaranteed...