ICS9173B

ICS9173B is VIDEO GENLOCK PLL manufactured by Renesas.

VIDEO GENLOCK PLL

Description

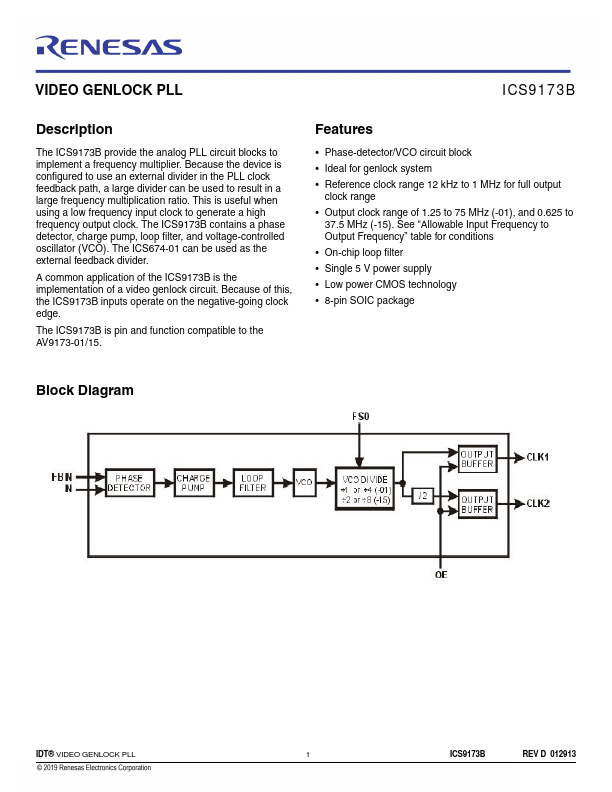

The ICS9173B provide the analog PLL circuit blocks to implement a frequency multiplier. Because the device is configured to use an external divider in the PLL clock feedback path, a large divider can be used to result in a large frequency multiplication ratio. This is useful when using a low frequency input clock to generate a high frequency output clock. The ICS9173B contains a phase detector, charge pump, loop filter, and voltage-controlled oscillator (VCO). The ICS674-01 can be used as the external feedback divider.

A mon application of the ICS9173B is the implementation of a video genlock circuit. Because of this, the ICS9173B...