ICS9248-81

ICS9248-81 is Frequency Generator & Integrated Buffer manufactured by Renesas.

ICS9248- 81

Frequency Generator & Integrated Buffers

General Description

The ICS9248-81 is the single chip clock solution for Desktop/ Notebook designs using the SIS style chipset. It provides all necessary clock signals for such a system.

Spread spectrum may be enabled through I2C programming. Spread spectrum typically reduces system EMI by 8d B to 10d B. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9248-81 employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature variations.

Serial programming I2C interface allows changing functions, stop clock programming and frequency selection. The SD_SEL latched input allows the SDRAM frequency to follow the CPUCLK frequency(SD_SEL=1) or other clock frequencies (SD_SEL=0)

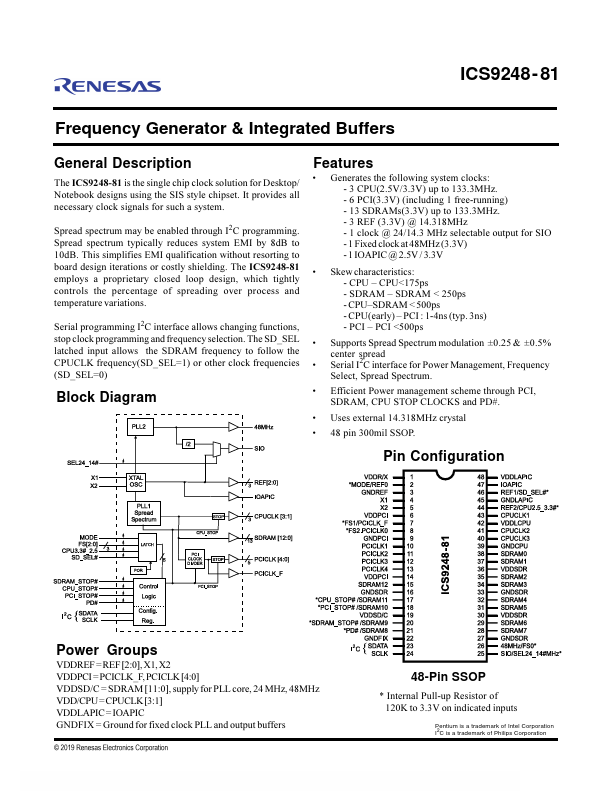

Block Diagram

Features

Generates the following system clocks:

- 3 CPU(2.5V/3.3V) up to 133.3MHz.

- 6 PCI(3.3V) (including 1 free-running)

- 13 SDRAMs(3.3V) up to 133.3MHz.

- 3 REF (3.3V) @ 14.318MHz

- 1 clock @ 24/14.3 MHz selectable output for SIO

- 1 Fixed clock at 48MHz (3.3V)

- 1 IOAPIC @ 2.5V / 3.3V

Skew characteristics:

- CPU CPU<175ps

- SDRAM SDRAM < 250ps

- CPUSDRAM < 500ps

- CPU(early) PCI : 1-4ns (typ. 3ns)

- PCI PCI <500ps

Supports Spread Spectrum modulation ±0.25 & ±0.5% center spread

Serial I2C interface for Power Management, Frequency Select, Spread Spectrum.

Efficient Power management scheme through PCI, SDRAM, CPU STOP CLOCKS and PD#.

Uses external 14.318MHz crystal

48 pin 300mil SSOP.

Pin Configuration

Power Groups

VDDREF = REF [2:0], X1, X2 VDDPCI = PCICLK_F, PCICLK [4:0] VDDSD/C = SDRAM [11:0], supply for PLL core, 24 MHz, 48MHz VDD/CPU = CPUCLK [3:1] VDDLAPIC = IOAPIC GNDFIX = Ground for fixed clock PLL and output...