ICS9FG1201H

Description

The ICS9FG1201H follows the Intel DB1200G Rev 1.0 Differential Buffer Specification. This buffer provides 12 output clocks for CPU Host Bus, PCI-Express, or Fully Buffered DIMM applications.

Key Features

- Drives 2 channels of 4 FBDIMMs (total of 8 FBDIMMs)

- Power up default is all outputs in 1:1 mode

- DIF_(9:0) can be “gear-shifted” from the input CPU Host Clock

- DIF_(11:10) can be “gear-shifted” from the input CPU Host Clock

- Spread spectrum compatible

- Supports output clock frequencies up to 400 MHz

- 8 Selectable SMBus addresses

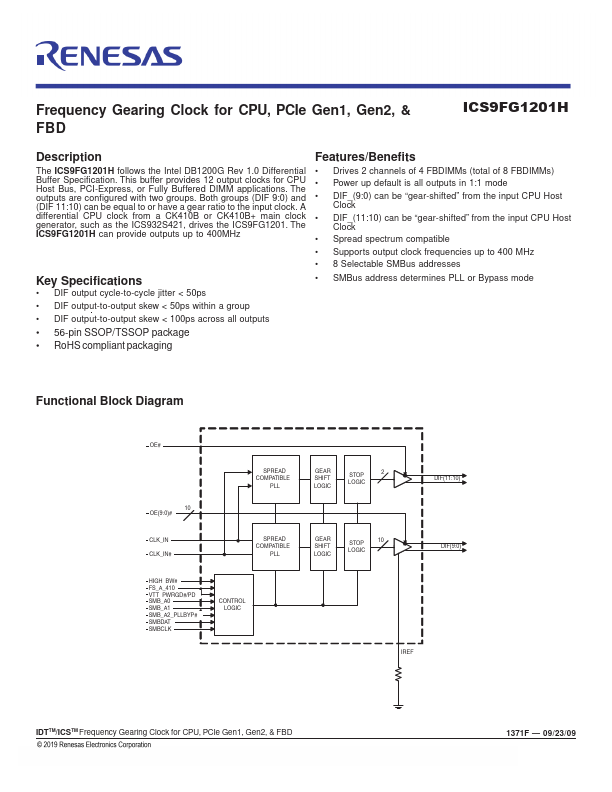

- SMBus address determines PLL or Bypass mode Functional Block Diagram OE# OE(9:0)# 10