IDT72225LB

IDT72225LB is CMOS SyncFIFO manufactured by Renesas.

- Part of the IDT72205LB comparator family.

- Part of the IDT72205LB comparator family.

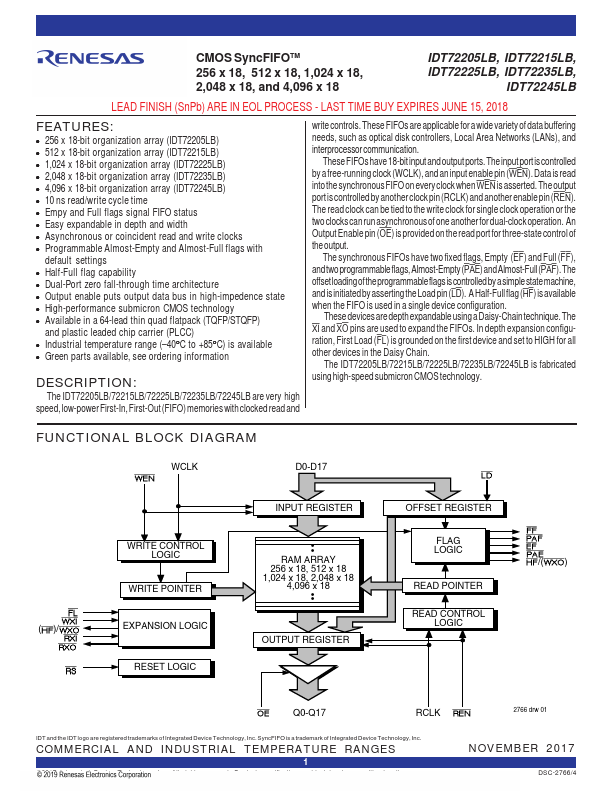

CMOS Sync FIFOTM 256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18, and 4,096 x 18

IDT72205LB, IDT72215LB, IDT72225LB, IDT72235LB,

IDT72245LB

LEAD FINISH (Sn Pb) ARE IN EOL PROCESS

- LAST TIME BUY EXPIRES JUNE 15, 2018

Features

:

- 256 x 18-bit organization array (IDT72205LB)

- 512 x 18-bit organization array (IDT72215LB)

- 1,024 x 18-bit organization array (IDT72225LB)

- 2,048 x 18-bit organization array (IDT72235LB)

- 4,096 x 18-bit organization array (IDT72245LB)

- 10 ns read/write cycle time

- Empy and Full flags signal FIFO status

- Easy expandable in depth and width

- Asynchronous or coincident read and write clocks

- Programmable Almost-Empty and Almost-Full flags with default settings

- Half-Full flag capability

- Dual-Port zero fall-through time architecture

- Output enable puts output data bus in high-impedence state

- High-performance submicron CMOS technology

- Available in a 64-lead thin quad flatpack (TQFP/STQFP) and plastic leaded chip carrier (PLCC)

- Industrial temperature range (- 40°C to +85°C) is available

- Green parts available, see ordering information

DESCRIPTION:

The IDT72205LB/72215LB/72225LB/72235LB/72245LB are very high speed, low-power First-In, First-Out (FIFO) memories with clocked read and write controls. These FIFOs are applicable for a wide variety of data buffering needs, such as optical disk controllers, Local Area Networks (LANs), and interprocessor munication.

These FIFOs have 18-bit input and output ports. The input port is controlled by a free-running clock (WCLK), and an input enable pin (WEN). Data is read into the synchronous FIFO on every clock when WEN is asserted. The output port is controlled by another clock pin (RCLK) and another enable pin (REN). The read clock can be tied to the write clock for single clock operation or the two clocks can run asynchronous of one another for dual-clock operation. An Output Enable pin (OE) is provided on the read port for three-state control of the output.

The synchronous FIFOs have two...