IDT72V3631

IDT72V3631 is 3.3 VOLT CMOS FIFO manufactured by Renesas.

3.3 VOLT CMOS Sync FIFOTM 512 x 36 1,024 x 36

IDT72V3631 IDT72V3641

Features

- Storage capacity: IDT72V3631

- 512 x 36 IDT72V3641

- 1,024 x 36

- Supports clock frequencies up to 67 MHz

- Fast access times of 10ns

- Free-running CLKA and CLKB can be asynchronous or coinci- dent (permits simultaneous reading and writing of data on a single clock edge)

- Clocked FIFO buffering data from Port A to Port B

- Synchronous read retransmit capability

- Mailbox register in each direction

- Programmable Almost-Full and Almost-Empty flags

- Microprocessor interface control logic

- Input Ready (IR) and Almost-Full (AF) flags synchronized by CLKA

- Output Ready (OR) and Almost-Empty (AE) flags synchronized by CLKB

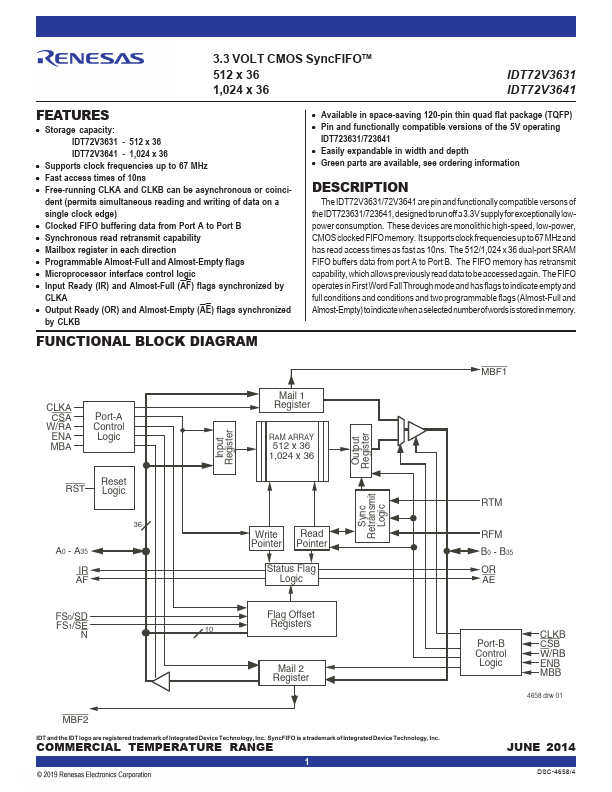

FUNCTIONAL BLOCK DIAGRAM

- Available in space-saving 120-pin thin quad flat package (TQFP)

- Pin and functionally patible versions of the 5V operating

IDT723631/723641

- Easily expandable in width and depth

- Green parts are available, see ordering information

DESCRIPTION

The IDT72V3631/72V3641 are pin and functionally patible versons of the IDT723631/723641, designed to run off a 3.3V supply for exceptionally lowpower consumption. These devices are monolithic high-speed, low-power, CMOS clocked FIFO memory. It supports clock frequencies up to 67 MHz and has read access times as fast as 10ns. The 512/1,024 x 36 dual-port SRAM FIFO buffers data from port A to Port B. The FIFO memory has retransmit capability, which allows previously read data to be accessed again. The FIFO operates in First Word Fall Through mode and has flags to indicate empty and full conditions and conditions and two programmable flags (Almost-Full and Almost-Empty) to indicate when a selected number of words is stored in memory.

CLKA CSA

W/RA ENA MBA

Port-A Control Logic

Mail 1 Register

RAM ARRAY

512 x 36 1,024 x...