IDT74ALVCH16721 Overview

Description

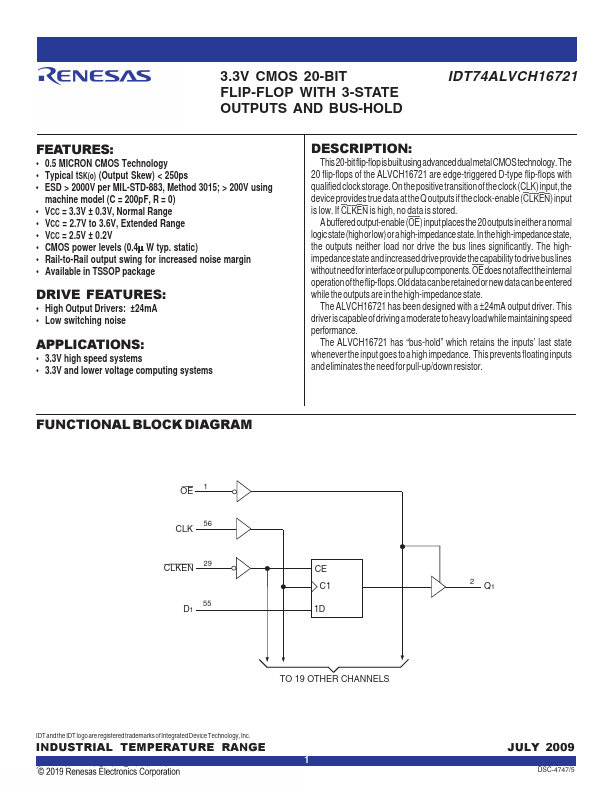

This 20-bit flip-flop is built using advanced dual metal CMOS technology. The 20 flip-flops of the ALVCH16721 are edge-triggered D-type flip-flops with qualified clock storage.

Key Features

- 0.5 MICRON CMOS Technology

- Typical tSK(o) (Output Skew) < 250ps

- ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R =

- VCC = 3.3V ± 0.3V, Normal Range

- VCC = 2.7V to 3.6V, Extended Range

- VCC = 2.5V ± 0.2V

- CMOS power levels (0.4μ W typ. static)

- Rail-to-Rail output swing for increased noise margin

- Available in TSSOP package DRIVE FEATURES

- High Output Drivers: ±24mA