IDTF1951

Overview

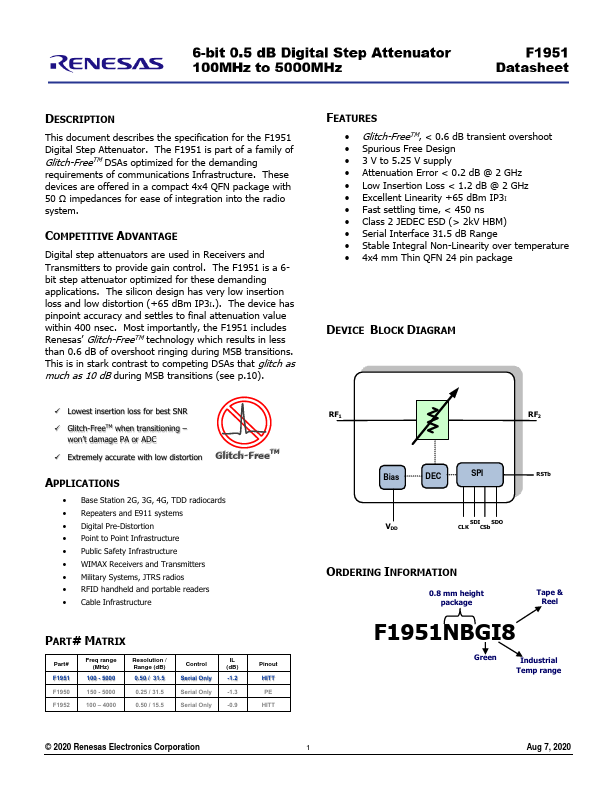

This document describes the specification for the F1951 Digital Step Attenuator. The F1951 is part of a family of Glitch-FreeTM DSAs optimized for the demanding requirements of communications Infrastructure.

- Glitch-FreeTM, < 0.6 dB transient overshoot

- Spurious Free Design

- 3 V to 5.25 V supply

- Attenuation Error < 0.2 dB @ 2 GHz

- Low Insertion Loss < 1.2 dB @ 2 GHz

- Excellent Linearity +65 dBm IP3I

- Fast settling time, < 450 ns

- Class 2 JEDEC ESD (> 2kV HBM)

- Serial Inte