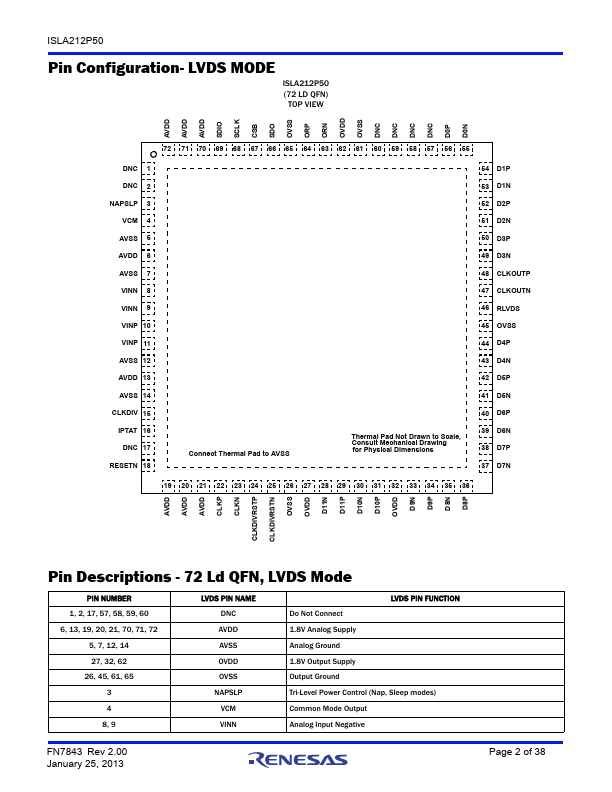

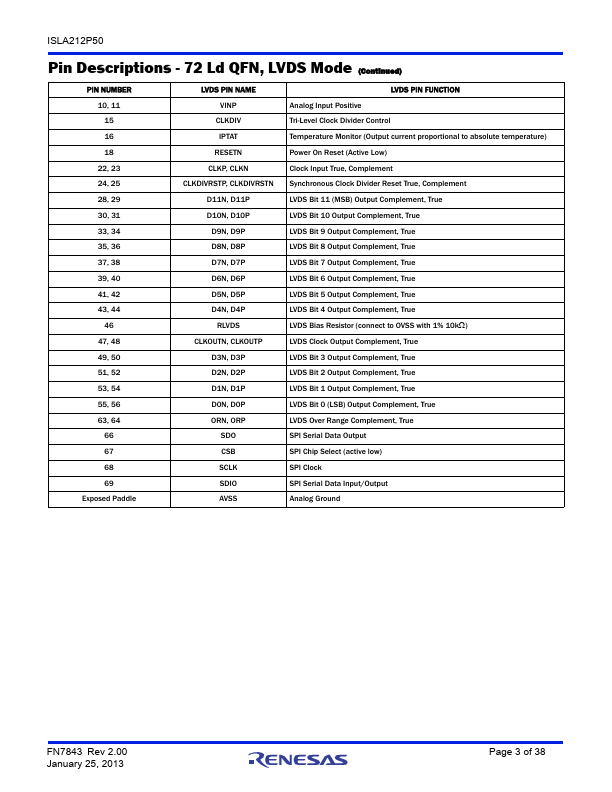

ISLA212P50 Description

ISLA212P50 12-Bit, 500MSPS ADC The ISLA212P50 is a 12-bit, 500MSPS analog-to-digital converter designed with Intersil’s proprietary FemtoCharge™ technology on a standard CMOS process. The ISLA212P50 is part of a pin-patible portfolio of 12 to 16-bit A/Ds with maximum sample rates ranging from 130MSPS to 500MSPS. The device utilizes two time-interleaved 250MSPS unit ADCs to achieve the ultimate sample rate of 500MSPS.

ISLA212P50 Key Features

- Automatic fine interleave correction calibration

- Single supply 1.8V operation

- Clock duty cycle stabilizer

- 75f clock jitter

- 700MHz bandwidth

- Programmable built-in test patterns

- Multi-ADC support

- SPI programmable fine gain and offset control

- Support for multiple ADC synchronization

- Optimized output timing