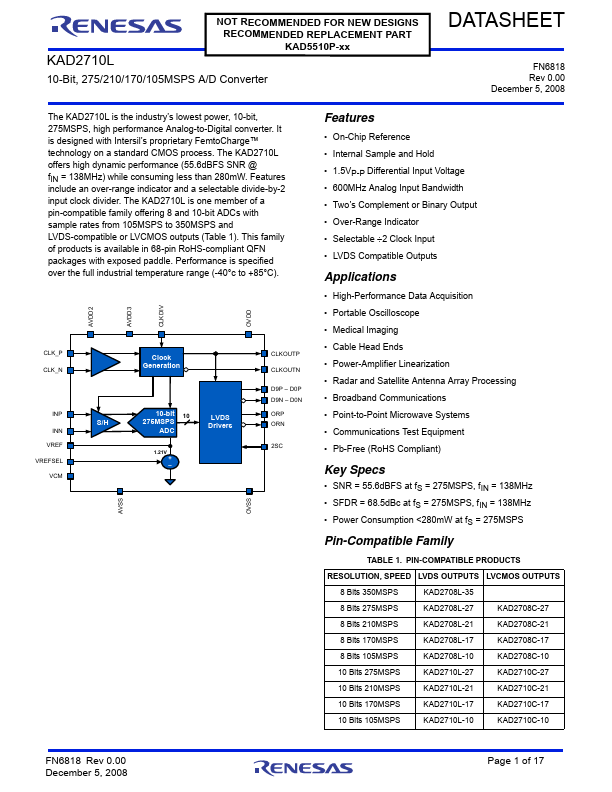

KAD2710L Overview

It is designed with Intersil’s proprietary FemtoCharge™ technology on a standard CMOS process. The KAD2710L offers high dynamic performance (55.6dBFS SNR @ fIN = 138MHz) while consuming less than 280mW.

KAD2710L Key Features

- CLKOUTP CLKOUTN

- D0P D9N

- D0N ORP ORN

- On-Chip Reference

- Internal Sample and Hold

- 1.5VP-P Differential Input Voltage

- 600MHz Analog Input Bandwidth

- Two’s plement or Binary Output

- Over-Range Indicator

- Selectable 2 Clock Input