MK74CG117A Overview

Description

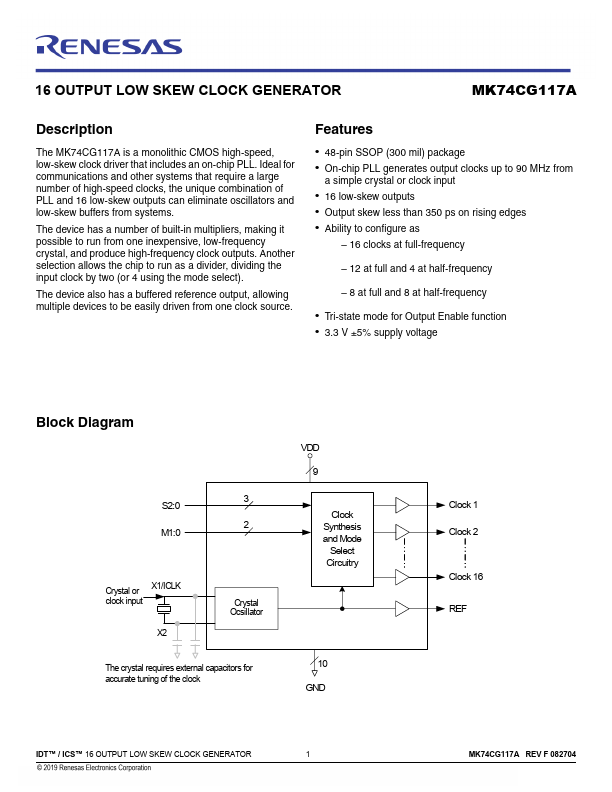

The MK74CG117A is a monolithic CMOS high-speed, low-skew clock driver that includes an on-chip PLL. Ideal for communications and other systems that require a large number of high-speed clocks, the unique combination of PLL and 16 low-skew outputs can eliminate oscillators and low-skew buffers from systems.

Key Features

- 48-pin SSOP (300 mil) package

- On-chip PLL generates output clocks up to 90 MHz from a simple crystal or clock input

- 16 low-skew outputs

- Output skew less than 350 ps on rising edges

- Ability to configure as – 16 clocks at full-frequency – 12 at full and 4 at half-frequency – 8 at full and 8 at half-frequency

- Tri-state mode for Output Enable function

- 3.3 V ±5% supply voltage