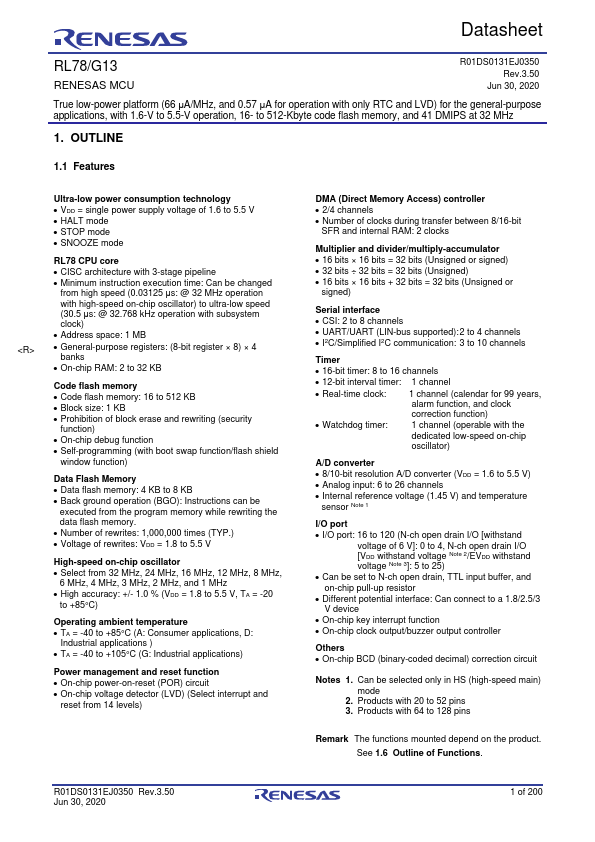

R5F101GDANA

Key Features

- VDD = single power supply voltage of 1.6 to 5.5 V

- SNOOZE mode RL78 CPU core

- CISC architecture with 3-stage pipeline

- Address space: 1 MB <R>

- General-purpose registers: (8-bit register ×

- On-chip RAM: 2 to 32 KB Code flash memory

- Code flash memory: 16 to 512 KB

- Block size: 1 KB

- Prohibition of block erase and rewriting (security function)

- On-chip debug function