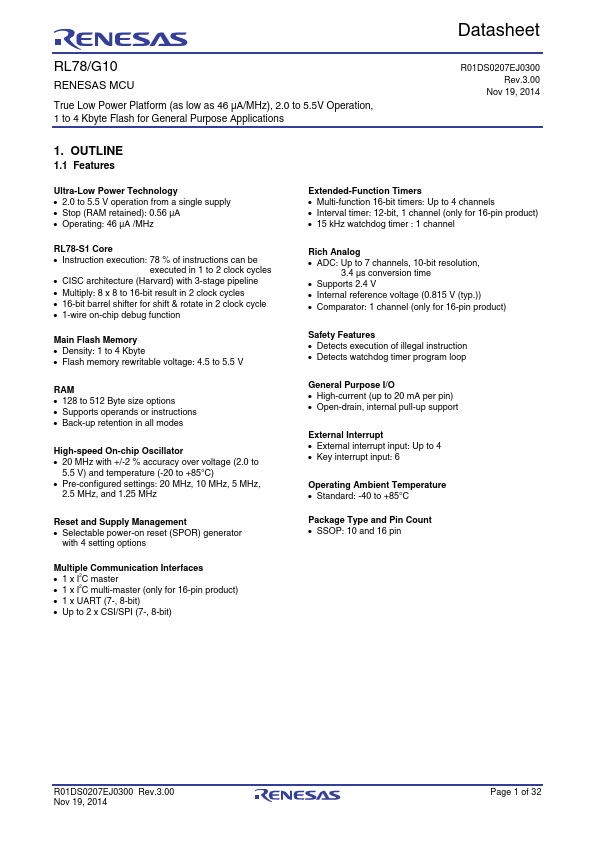

R5F10Y44

Overview

- 2.0 to 5.5 V operation from a single supply

- Stop (RAM retained): 0.56 µA

- Operating: 46 µA /MHz RL78-S1 Core

- Instruction execution: 78 % of instructions can be executed in 1 to 2 clock cycles

- CISC architecture (Harvard) with 3-stage pipeline

- Multiply: 8 x 8 to 16-bit result in 2 clock cycles

- 16-bit barrel shifter for shift & rotate in 2 clock cycle

- 1-wire on-chip debug function Main Flash Memory

- Density: 1 to 4 Kbyte

- Flash memory rewritable voltage: 4.5 to 5.5 V RAM