R5F51303ADFL

R5F51303ADFL is 32-bit RX MCUs manufactured by Renesas.

- Part of the R5F51305ADFN comparator family.

- Part of the R5F51305ADFN comparator family.

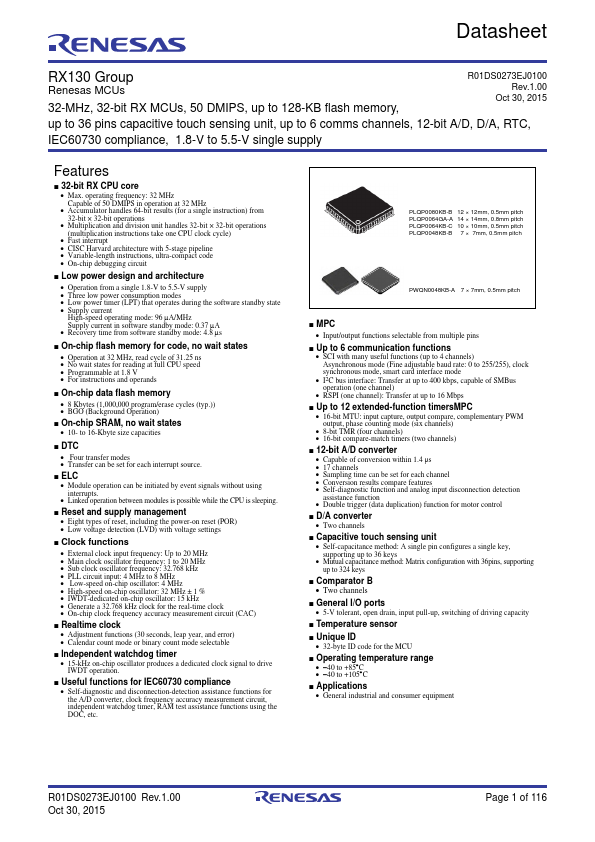

RX130 Group

Renesas MCUs

32-MHz, 32-bit RX MCUs, 50 DMIPS, up to 128-KB flash memory,

R01DS0273EJ0100 Rev.1.00

Oct 30, 2015 up to 36 pins capacitive touch sensing unit, up to 6 ms channels, 12-bit A/D, D/A, RTC,

IEC60730 pliance, 1.8-V to 5.5-V single supply

Features

- 32-bit RX CPU core

- Max. operating frequency: 32 MHz Capable of 50 DMIPS in operation at 32 MHz

- Accumulator handles 64-bit results (for a single instruction) from 32-bit × 32-bit operations

- Multiplication and division unit handles 32-bit × 32-bit operations (multiplication instructions take one CPU clock cycle)

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length...