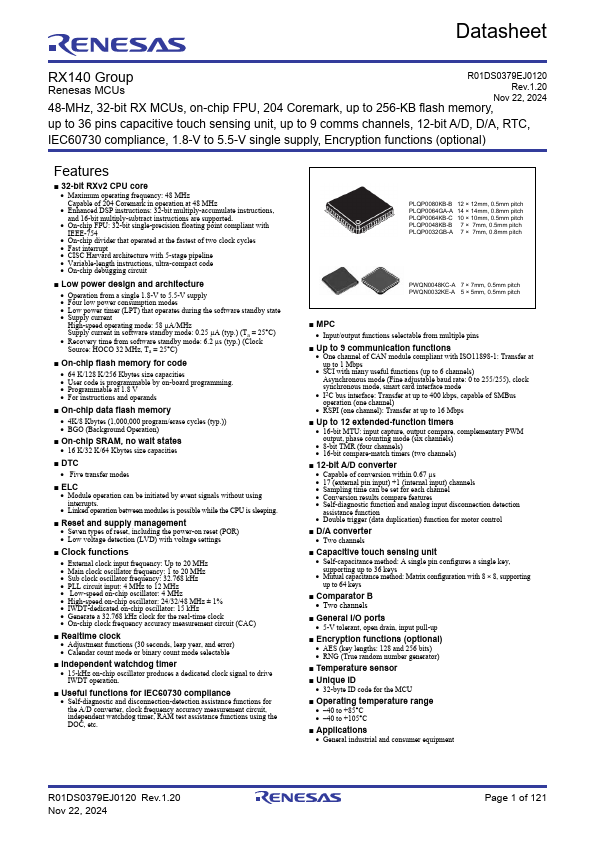

R5F51406BDNE

R5F51406BDNE is 32-bit RX MCU manufactured by Renesas.

- Part of the R5F51406ADFN comparator family.

- Part of the R5F51406ADFN comparator family.

Features

- 32-bit RXv2 CPU core

- Maximum operating frequency: 48 MHz Capable of 204 Coremark in operation at 48 MHz

- Enhanced DSP instructions: 32-bit multiply-accumulate instructions, and 16-bit multiply-subtract instructions are supported.

- On-chip FPU: 32-bit single-precision floating point pliant with IEEE-754

- On-chip divider that operated at the fastest of two clock cycles

- Fast interrupt

- CISC Harvard architecture with 5-stage pipeline

- Variable-length instructions, ultra-pact code

- On-chip debugging circuit

- Low power design and architecture

- Operation from a single 1.8-V to 5.5-V supply

- Four low power consumption modes

- Low power timer (LPT) that operates during the software standby state

- Supply current High-speed operating mode: 58 µA/MHz Supply current in software standby mode: 0.25 µA (typ.) (Ta = 25°C)

- Recovery time from software standby mode: 6.2 µs (typ.) (Clock Source: HOCO 32 MHz, Ta = 25°C)

- On-chip flash memory for code

- 64 K/128 K/256 Kbytes size capacities

- User code is programmable by on-board programming.

- Programmable at 1.8 V

- For instructions and operands

- On-chip data flash memory

- 4K/8 Kbytes (1,000,000 program/erase cycles (typ.))

- BGO (Background Operation)

- On-chip SRAM, no wait states

- 16 K/32 K/64 Kbytes size capacities

- DTC

- Five transfer modes

- ELC

- Module operation can be initiated by event signals without using interrupts.

- Linked operation between modules is possible while the CPU is sleeping.

- Reset and supply management

- Seven types of reset, including the power-on reset (POR)

- Low voltage detection (LVD) with voltage settings

- Clock functions

- External clock input frequency: Up to 20 MHz

- Main clock oscillator frequency: 1 to 20 MHz

- Sub clock oscillator frequency: 32.768 k Hz

- PLL circuit input: 4 MHz to 12 MHz

- Low-speed on-chip oscillator: 4...