R5F563TEBDFA

R5F563TEBDFA is manufactured by Renesas.

Features

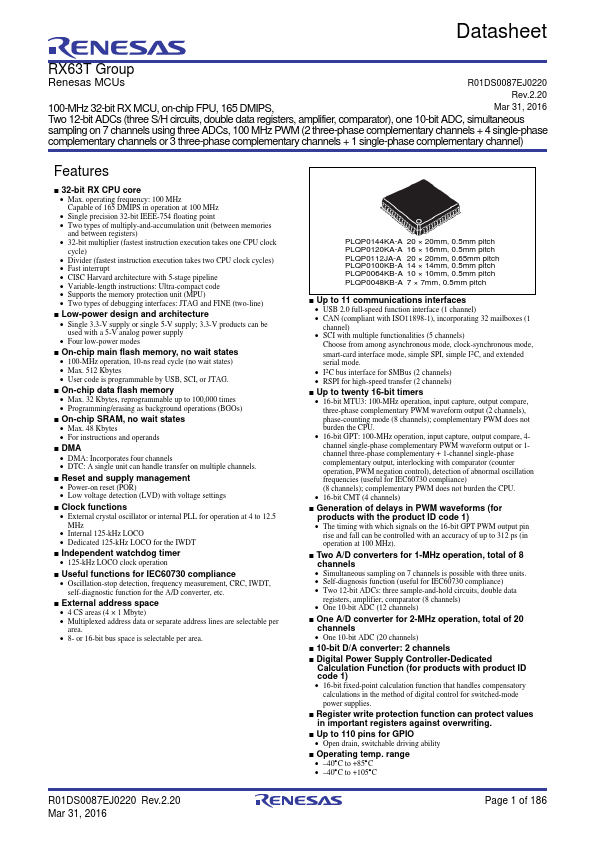

RX63T Group

Renesas MCUs

R01DS0087EJ0220

Rev.2.20

100-MHz 32-bit RX MCU, on-chip FPU, 165 DMIPS,

Mar 31, 2016

Two 12-bit ADCs (three S/H circuits, double data registers, amplifier, parator), one 10-bit ADC, simultaneous sampling on 7 channels using three ADCs, 100 MHz PWM (2 three-phase plementary channels + 4 single-phase plementary channels or 3 three-phase plementary channels + 1 single-phase plementary channel)

Features

- 32-bit RX CPU core

- Max. operating frequency: 100 MHz Capable of 165 DMIPS in operation at 100 MHz

- Single precision 32-bit IEEE-754 floating point

- Two types of multiply-and-accumulation unit (between memories and...