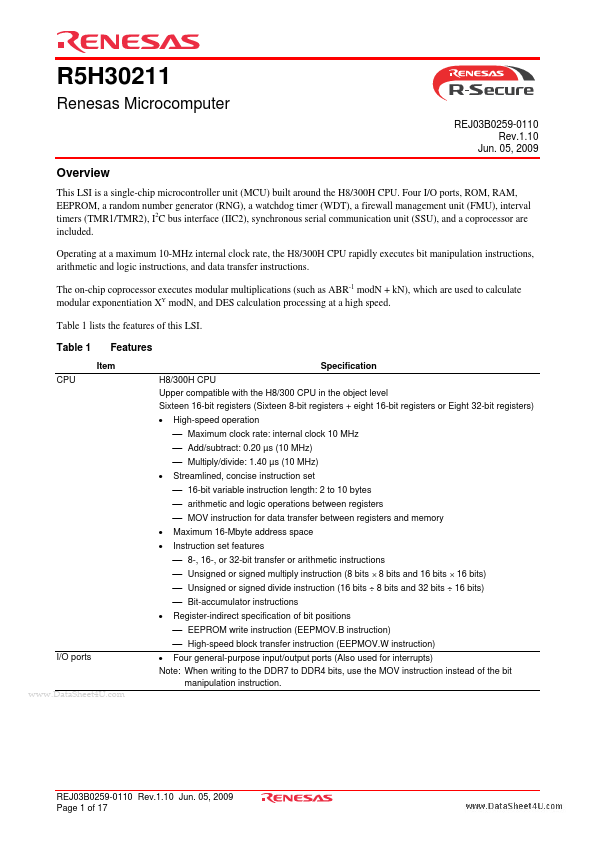

R5H30211

R5H30211 is Microcomputer manufactured by Renesas.

Renesas Microputer

REJ03B0259-0110 Rev.1.10 Jun. 05, 2009

Overview

This LSI is a single-chip microcontroller unit (MCU) built around the H8/300H CPU. Four I/O ports, ROM, RAM, EEPROM, a random number generator (RNG), a watchdog timer (WDT), a firewall management unit (FMU), interval timers (TMR1/TMR2), I2C bus interface (IIC2), synchronous serial munication unit (SSU), and a coprocessor are included. Operating at a maximum 10-MHz internal clock rate, the H8/300H CPU rapidly executes bit manipulation instructions, arithmetic and logic instructions, and data transfer instructions. The on-chip coprocessor executes modular multiplications (such as ABR-1 modN + kN), which are...