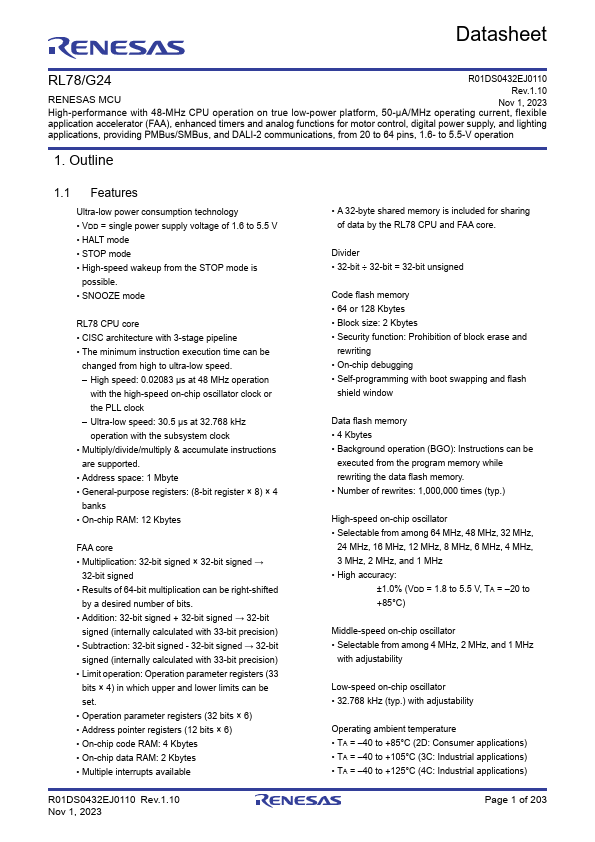

R7F101GJE

Features

Ultra-low power consumption technology

- VDD = single power supply voltage of 1.6 to 5.5 V

- HALT mode

- STOP mode

- High-speed wakeup from the STOP mode is possible.

- SNOOZE mode

RL78 CPU core

- CISC architecture with 3-stage pipeline

- The minimum instruction execution time can be changed from high to ultra-low speed.

- High speed: 0.02083 µs at 48 MHz operation with the high-speed on-chip oscillator clock or the PLL clock

- Ultra-low speed: 30.5 µs at 32.768 k Hz operation with the subsystem clock

- Multiply/divide/multiply & accumulate instructions are supported.

- Address space: 1 Mbyte

- General-purpose registers: (8-bit register × 8) × 4 banks

- On-chip RAM: 12 Kbytes

FAA core

- Multiplication: 32-bit signed × 32-bit signed →

32-bit signed

- Results of 64-bit multiplication can be right-shifted by a desired number of bits.

- Addition: 32-bit signed + 32-bit signed → 32-bit signed (internally calculated with 33-bit precision)

- Subtraction: 32-bit signed

- 32-bit signed...