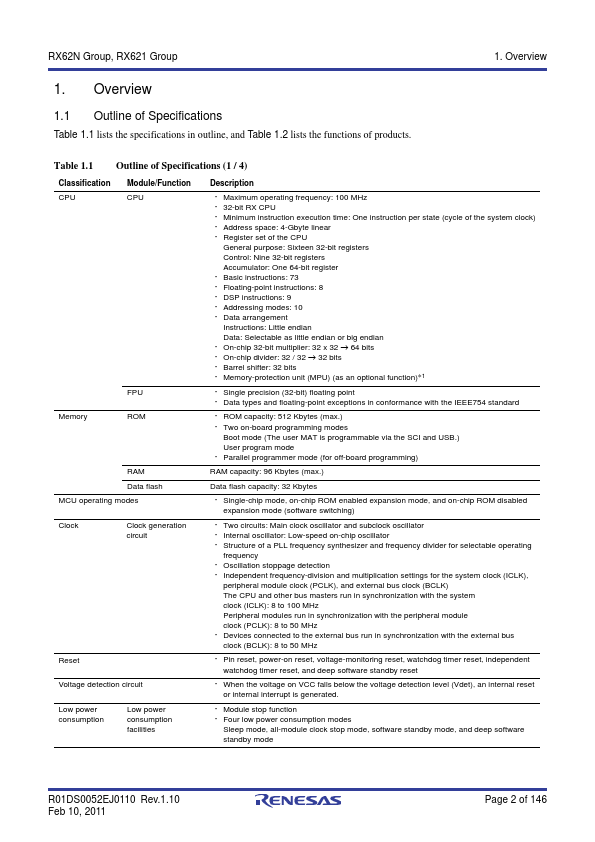

RX62N Description

Control, Interrupt, Bulk, Isochronous (1) Ethernet MAC 10/100 Mbps, Half or Full Duplex Supported. Dedicated DMA with 2-Kbyte transmit and receive FIFOs. RMII or MII interface to external PHY (1) CAN ISO11898-1, supports 32 mailboxes (6) SCI channels:.

RX62N Key Features

- 32-bit RX CPU Core

- Delivers 165 DMIPS at a maximum operating frequency of 100 MHz

- Single Precision 32-bit IEEE-754 Floating Point

- Accumulator: 32 × 32 to 64-bit result, one instruction

- Mult/Divide Unit, 32 × 32 Multiply in one CPU clock for multiple instructions

- Interrupt response in as few as 5 CPU clock cycles

- CISC-Harvard Architecture with 5-stage pipeline

- Variable length instructions, ultra pact code

- Supports the Memory Protection Unit (MPU)

- Background JTAG debug plus high-speed trace