RT3601BH

Description

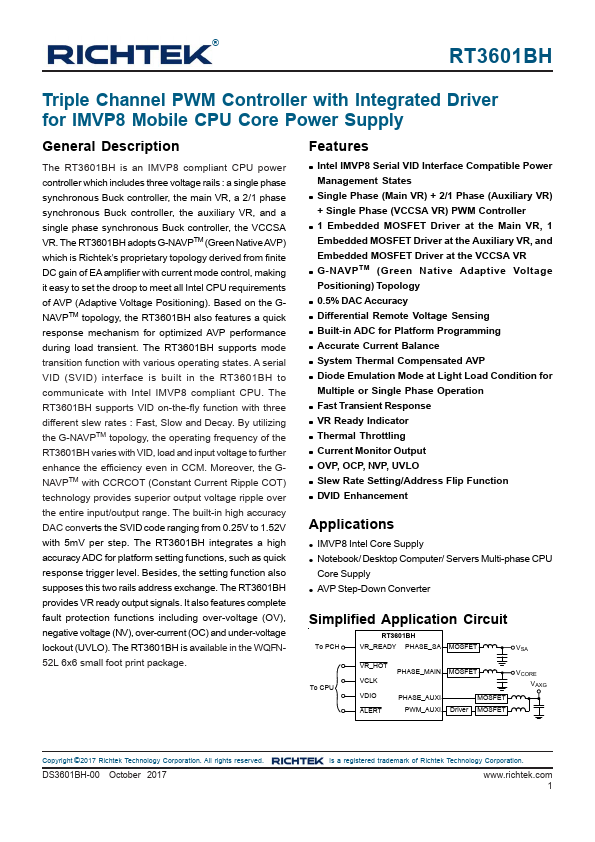

The RT3601BH is an IMVP8 compliant CPU power controller which includes three voltage rails : a single phase synchronous Buck controller, the main VR, a 2/1 phase synchronous Buck controller, the auxiliary VR, and a single phase synchronous Buck controller, the VCCSA VR. The RT3601BH adopts G-NAVPTM (Green Native AVP) which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all Intel CPU requirements of AVP (Adaptive Voltage Positioning).

Key Features

- Intel IMVP8 Serial VID Interface compatible Power Management States

- Single Phase (Main VR) + 2/1 Phase (Auxiliary VR) + Single Phase (VCCSA VR) PWM Controller

- 1 Embedded MOSFET Driver at the Main VR, 1 Embedded MOSFET Driver at the Auxiliary VR, and Embedded MOSFET Driver at the VCCSA VR

- G-NAVPTM (Green Native Adaptive Voltage Positioning) Topology

- 0.5% DAC Accuracy

- Differential Remote Voltage Sensing

- Built-in ADC for Platform Programming

- Accurate Current Balance

- Diode Emulation Mode at Light Load Condition for Multiple or Single Phase Operation

- Fast Transient Response