BU2624

BU2624 is PLL frequency synthesizer for tuners manufactured by ROHM.

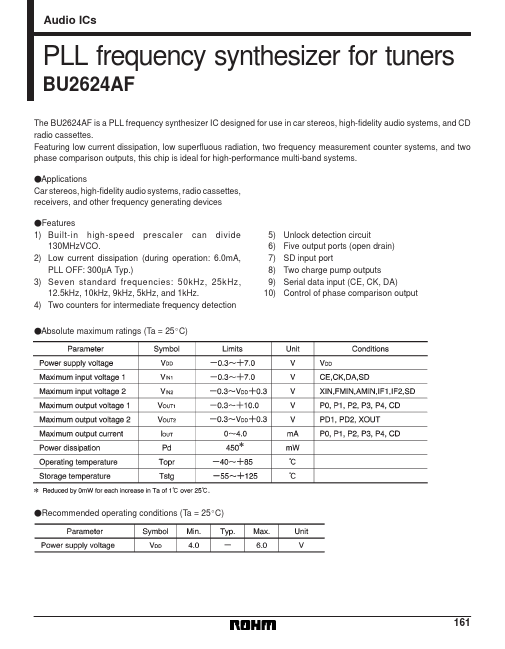

Audio ICs

PLL frequency synthesizer for tuners

BU2624AF

The BU2624AF is a PLL frequency synthesizer IC designed for use in car stereos, high-fidelity audio systems, and CD radio cassettes. Featuring low current dissipation, low superfluous radiation, two frequency measurement counter systems, and two phase parison outputs, this chip is ideal for high-performance multi-band systems. FApplications Car stereos, high-fidelity audio systems, radio cassettes, receivers, and other frequency generating devices FFeatures 1) Built-in high-speed prescaler can divide 130MHz VCO. 2) Low current dissipation (during operation: 6.0m A, PLL OFF: 300µA Typ.) 3) Seven standard frequencies: 50k Hz, 25k Hz, 12.5k Hz, 10k Hz, 9k Hz, 5k Hz, and 1k Hz. 4) Two counters for intermediate frequency detection FAbsolute maximum ratings (Ta = 25_C)

5) 6) 7) 8) 9) 10)

Unlock detection circuit Five output ports (open drain) SD input port Two charge pump outputs Serial data input (CE, CK, DA) Control of phase parison output

FRemended operating conditions (Ta = 25_C)

Audio ICs

FBlock diagram

BU2624AF

Audio ICs

FPin descriptions

BU2624AF

Audio ICs

FElectrical characteristics (unless otherwise noted, Ta = 25_C, VDD = 5.0V)

BU2624AF

Audio ICs

FCircuit operation Input data format

BU2624AF

Output data format

CE output is set to LO.

Audio ICs

BU2624AF

Explanation of the data (1) Division data: For D0 through D15 (When S = 1, use D4 through D15.)

(2)

(3) (4)

CT: Frequency measurement beginning data 1: Begins measurement. 0: Resets internal counter, IF1 and IF2 go to pul down. Output port control data: P0, P1, P2, P3, P4 PL PH: Control of charge pump output PH = 0, PL = 0 PLL operation PH = 0, PL = 1 PD1 PD2 LO level PH = 1, PL = 0 PD1 PD2 HI level PH = 1, PL = 1 PD1 PD2 LO level

(5)

R0, R1, R2, standard frequency data

(6) S: switch between FMIN and AMIN 0: FMIN 1: AMIN (7) PS: If this bit is set to ON while AMIN is selected, swallow counter division is possible. (8)...