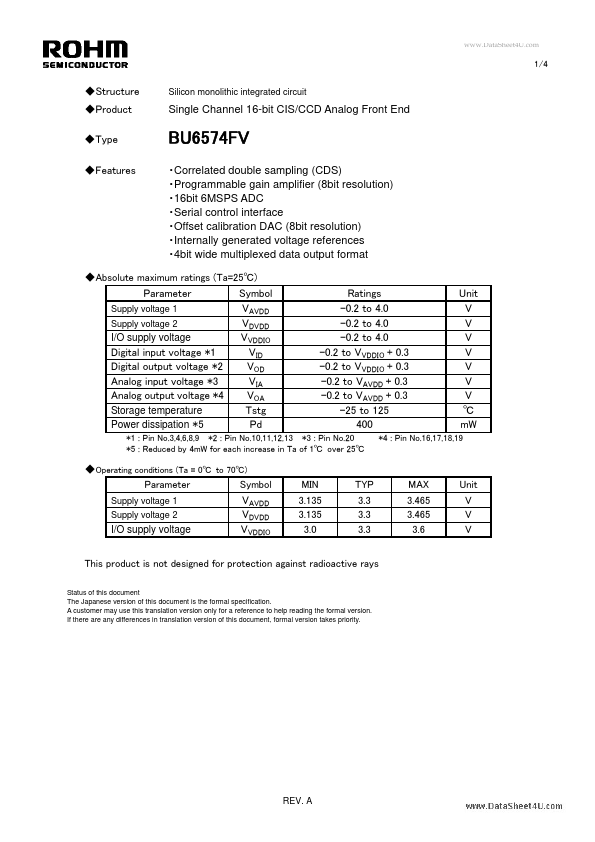

BU6574FV

BU6574FV is Silicon monolithic integrated circuit manufactured by ROHM.

Features

Silicon monolithic integrated circuit

Single Channel 16-bit CIS/CCD Analog Front End

- Correlated double sampling (CDS)

- Programmable gain amplifier (8bit resolution)

- 16bit 6MSPS ADC

- Serial control interface

- Offset calibration DAC (8bit resolution)

- Internally generated voltage references

- 4bit wide multiplexed data output format Ratings -0.2 to 4.0 -0.2 to 4.0 -0.2 to 4.0 -0.2 to VVDDIO + 0.3 -0.2 to VVDDIO + 0.3 -0.2 to VAVDD + 0.3 -0.2 to VAVDD + 0.3 -25 to 125 400 Unit V V V V V V V ℃ m W

- Absolute maximum ratings (Ta=25℃) Parameter Symbol Supply voltage 1 VAVDD Supply voltage 2 VDVDD I/O supply voltage VVDDIO Digital input voltage

- 1 VID Digital output voltage

- 2 VOD Analog input voltage

- 3 VIA Analog output voltage

- 4 VOA Storage temperature Tstg Power dissipation

- 5 Pd

- 1 : Pin No.3,4,6,8,9

- 2 : Pin No.10,11,12,13

- 3 : Pin No.20

- 5 : Reduced by 4m W for each increase in Ta of 1℃ over 25℃

- 4 : Pin No.16,17,18,19

- Operating conditions (Ta = 0℃ to 70℃) Parameter Symbol Supply voltage 1 VAVDD Supply voltage 2 VDVDD I/O supply voltage VVDDIO

MIN 3.135 3.135 3.0

TYP 3.3 3.3 3.3

MAX 3.465 3.465 3.6

Unit V V V

This product is not designed for protection against radioactive rays

Status of this document The Japanese version of this document is the formal specification. A customer may use this translation version only for a reference to help reading the formal version. If there are any differences in translation version of this document, formal version takes priority.

REV. A

..

2/4

- Electrical characteristics (Unless otherwise noted, VAVDD=VDVDD=VVDDIO = 3.3V, Ta = 25℃)

Parameter

Symbol

MIN 0.26 0.7- VVDDIO VVDDIO-0.5

- TYP 35.7 41.7 32 34 1.5 3.0 2.2 4.4 30

MAX 2.7 6 0.2- VVDDIO 1 1 0.5 70 50 10 10 60

Unit V MSPS V V u A u A V V m A m A m A m A u A

Conditions

Overall System Specification Input signal limits VIN Conversion Rate RATE Digital Inputs High level input voltage VIH Low level input voltage VIL High level input current IIH Low...