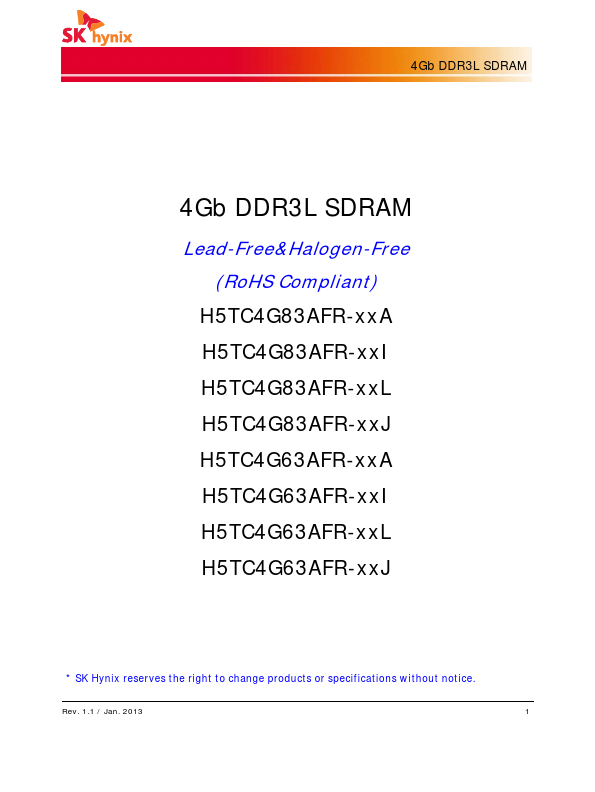

H5TC4G63AFR-xxI

H5TC4G63AFR-xxI is 4Gb DDR3L SDRAM manufactured by SK Hynix.

- Part of the H5TC4G83AFR-xxA comparator family.

- Part of the H5TC4G83AFR-xxA comparator family.

Description

The H5TC4G83AFR-xx A(I,L,J) and H5TC4G63AFR-xx A(I,L,J) are a 4Gb low power Double Data Rate III (DDR3L) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density, high bandwidth and low power operation at 1.35V. SK Hynix DDR3L SDRAM provides backward patibility with the 1.5V DDR3 based environment without any changes. SK Hynix 4Gb DDR3L SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the clock (falling edges of the clock), data, data strobes and write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 8-bit prefetched to achieve very high bandwidth.

Device Features and Ordering Information

FEATURES

- VDD=VDDQ=1.35V + 0.100 /

- 0.067V

- Fully differential clock inputs (CK, CK) operation

- Differential Data Strobe (DQS, DQS)

- On chip DLL align DQ, DQS and DQS transition with CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 6, 7, 8, 9, 10 and 11, 13 supported

- Programmable additive latency 0, CL-1, and CL-2 supported

- Programmable CAS Write latency (CWL) = 5, 6, 7, 8

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- BL switch on the fly

- 8banks

- Average Refresh Cycle (Tcase of 0 o C~ 95 o C)

- 7.8 µs at 0o C ~ 85 o C

- 3.9 µs at 85o C ~ 95 o C mercial Temperature( 0o C ~ 85 o C) Industrial Temperature( -40o C ~ 95 o C) http://../

- JEDEC standard 78ball FBGA(x8), 96ball FBGA (x16) Driver strength selected by EMRS

- Dynamic On Die Termination supported

- Asynchronous RESET pin supported

- ZQ calibration supported

- TDQS (Termination Data Strobe) supported (x8 only)

- Write Levelization supported

- 8 bit pre-fetch

-...