29DL32BF

29DL32BF is MBM29DL32BF manufactured by SPANSION.

DESCRIPTION

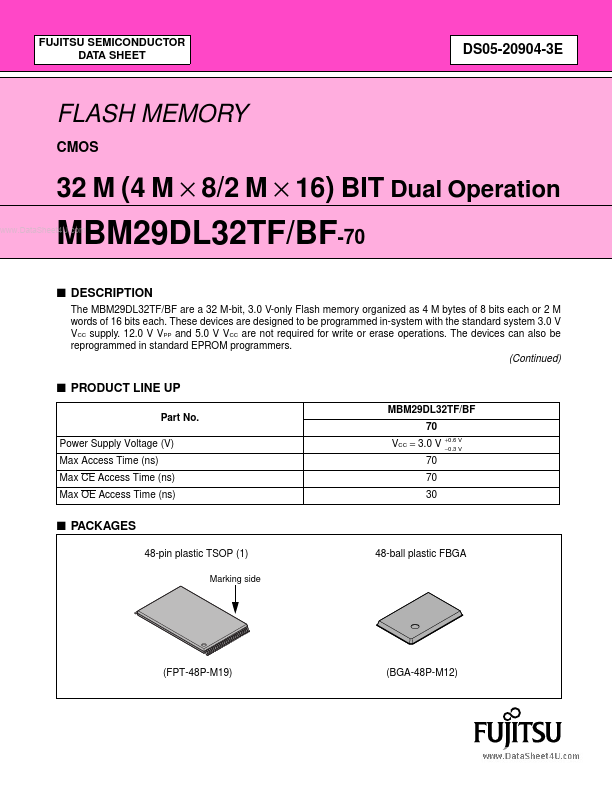

The MBM29DL32TF/BF are a 32 M-bit, 3.0 V-only Flash memory organized as 4 M bytes of 8 bits each or 2 M words of 16 bits each. These devices are designed to be programmed in-system with the standard system 3.0 V VCC supply. 12.0 V VPP and 5.0 V VCC are not required for write or erase operations. The devices can also be reprogrammed in standard EPROM programmers. (Continued) s PRODUCT LINE UP

Part No. Power Supply Voltage (V) Max Access Time (ns) Max CE Access Time (ns) Max OE Access Time (ns) MBM29DL32TF/BF 70 VCC = 3.0 V 70 70 30

+0.6 V

- 0.3 V s PACKAGES

48-pin plastic TSOP (1)

Marking side

48-ball plastic FBGA

(FPT-48P-M19)

(BGA-48P-M12)

MBM29DL32TF/BF-70

)

(Continued)

MBM29DL32TF/BF are organized into four physical banks; Bank A, Bank B, Bank C and Bank D, which are considered to be four separate memory arrays operations. It is the Fujitsu’s standard 3.0 V only Flash memories, with the additional capability of allowing a normal non-delayed read access from a non-busy bank of the array while an embedded write (either a program or an erase) operation is simultaneously taking place on the other bank. In the device, a new design concept called Flex Bank TM

- 1 Architecture is implemented. Using this concept the device can execute simultaneous operation between Bank 1, a bank chosen from among the four banks, and Bank 2, a bank consisting of the three remaining banks. This means that any bank can be chosen as Bank 1. (Refer to “1. Simultaneous Operation” in “s FUNCTIONAL DESCRIPTION

”.)

..

The standard device offers access time 70 ns, allowing operation of high-speed microprocessors without the wait. To eliminate bus contention the device has separate chip enable (CE) , write enable (WE) and output enable (OE) controls.

This device consists of pin and mand set patible with JEDEC standard E2PROMs. mands are written to the mand register using standard microprocessor write timings. Register contents serve as input to an internal state-machine which...