M34A02

M34A02 is 2 Kbit Serial SMBus EEPROM for ACR Card Configuration manufactured by STMicroelectronics.

DESCRIPTION

These electrically erasable programmable memory (EEPROM) devices are organized as 256x8 bits, and operate down to 2.7 V. These devices are available in Plastic Small Outline and Thin Shrink Small Outline packages. These devices are written by the ACR card-issuer, and then accessed in Read mode in the application, using the ACR Serial Bus protocol. This is a two wire serial interface that uses a bidirectional data bus and serial clock. The device carries a built-in 4-bit Device Type Identifier code (1011). The device behaves as a slave in the ACR Serial Bus protocol, with all memory operations synchronized by the serial clock. Read and Write operations are initiated by a Start condition, generated by the bus master. The Start condition

8 1

TSSOP8 (DW) 169 mil width

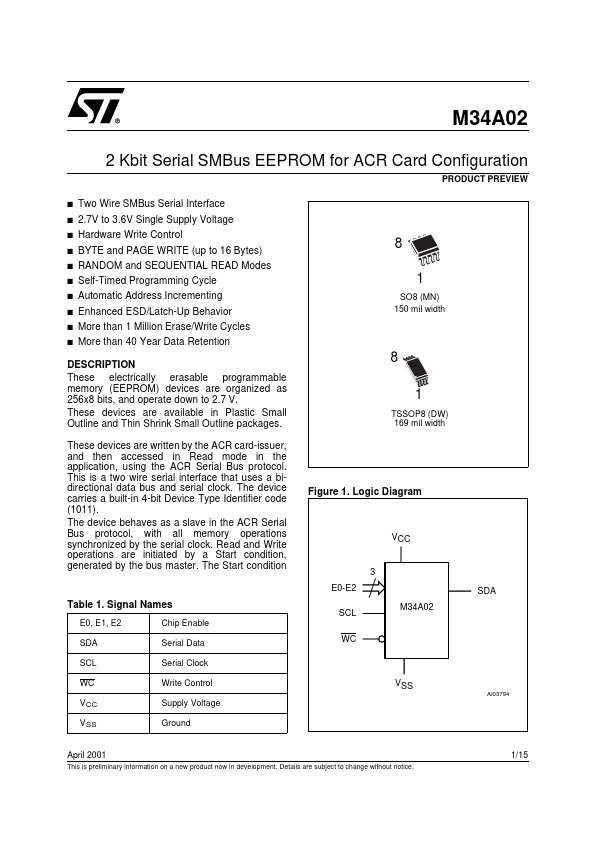

Figure 1. Logic Diagram

3 E0-E2 SDA M34A02

Table 1. Signal Names

E0, E1, E2 SDA SCL WC VCC VSS Chip Enable Serial Data Serial Clock Write Control Supply Voltage Ground

SCL WC

AI03794

April 2001

This is preliminary information on a new product now in development. Details are subject to change without notice.

1/15

Figure 2. SO and TSSOP Connections Figure 3. Typical ACR Application PCB Connection (showing E2,E1,E0 address 000)

VCC M34A02 E0 E1 E2 VSS 1 2 3 4 8 7 6 5

AI03795

E0 VCC WC SCL SDA E1 E2 VSS VSS

VCC WC SCL SDA RL

ACR Bus

AI04092

Note: 1. This arrangement on the chip enable lines allows the application to start at ACR address 000h. is followed by a Device Select code and RW bit (as described in Table 3), terminated by an acknowledge bit. When writing data to the memory, the device inserts an acknowledge bit during the 9th bit time, following the bus master’s 8-bit transmission. When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a No Ack for Read. Power On Reset: V CC Lock-Out Write Protect In order to prevent data...