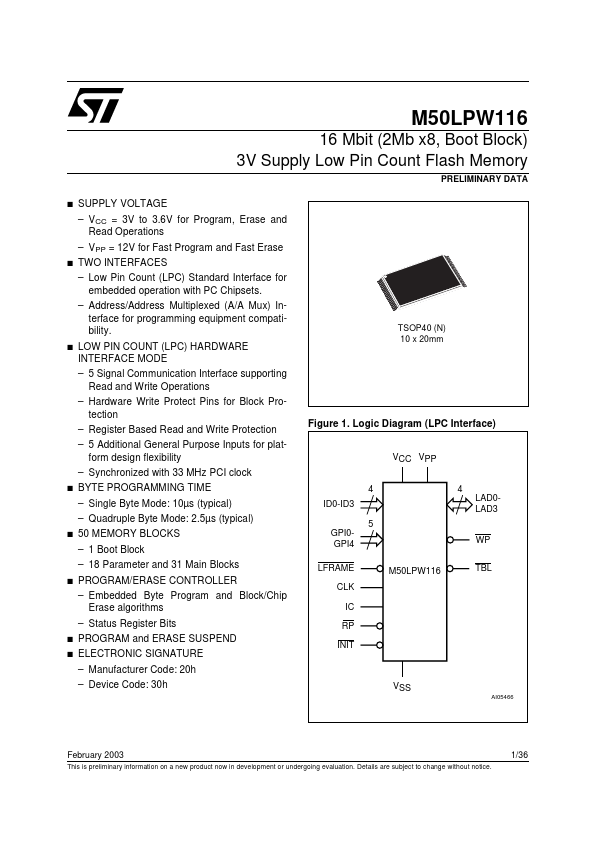

M50LPW116 Overview

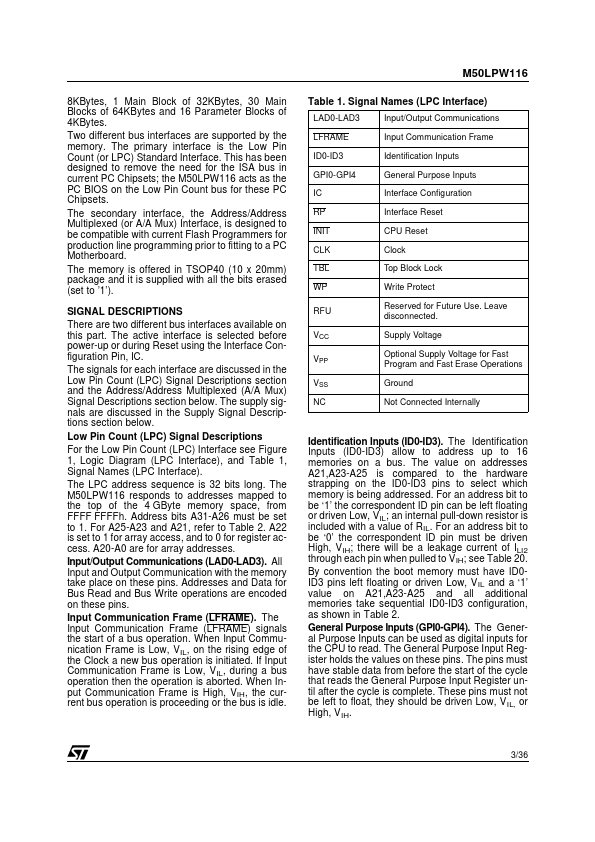

The M50LPW116 is a 16 Mbit (2Mb x8) nonvolatile memory that can be read, erased and reprogrammed. These operations can be performed using a single low voltage (3.0 to 3.6V) supply. For fast programming, and fast erasing, an optional 12V power supply can be used to reduce the programming and the erasing times.