M68AF511A

M68AF511A is 4 Mbit (512K x8) / 5V Asynchronous SRAM manufactured by STMicroelectronics.

FEATURES

SUMMARY s SUPPLY VOLTAGE: 4.5 to 5.5V s s s s s s

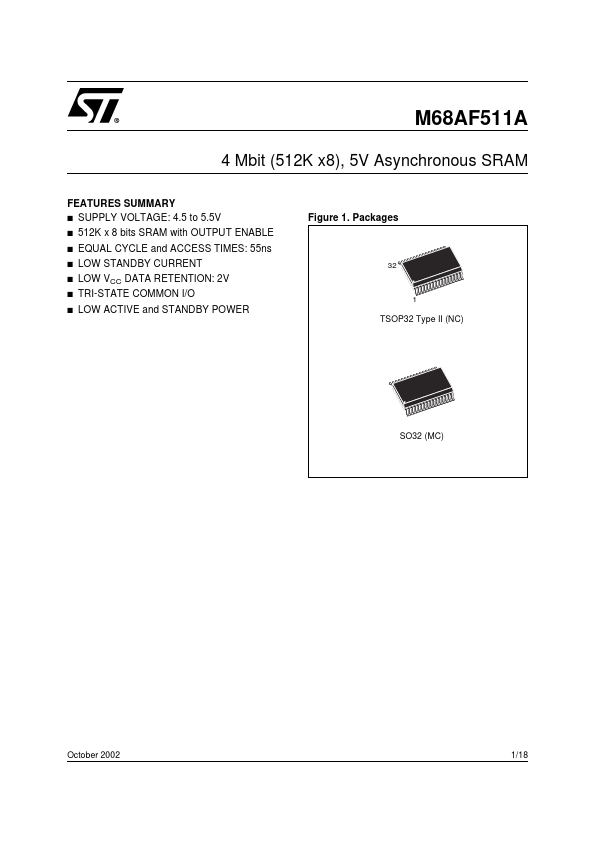

Figure 1. Packages

512K x 8 bits SRAM with OUTPUT ENABLE EQUAL CYCLE and ACCESS TIMES: 55ns LOW STANDBY CURRENT LOW VCC DATA RETENTION: 2V TRI-STATE MON I/O LOW ACTIVE and STANDBY POWER

TSOP32 Type II (NC)

SO32 (MC)

October 2002

1/18

TABLE OF CONTENTS SUMMARY DESCRIPTION

- -

- -

- -

- -

- -

- . . . . 3 Figure 2. Logic Diagram

- -

- Table 1. Signal Names

- -

- . Figure 3. TSOP and SO Connections

- Figure 4. Block Diagram

- -

- 3 3 4 5

MAXIMUM RATING-

- -

- -

- -

- -

- -

- - 5 Table 2. Absolute Maximum Ratings

- -

- -

- -

- -

- . . . . 5 DC AND AC PARAMETERS-

- -

- -

- -

-...