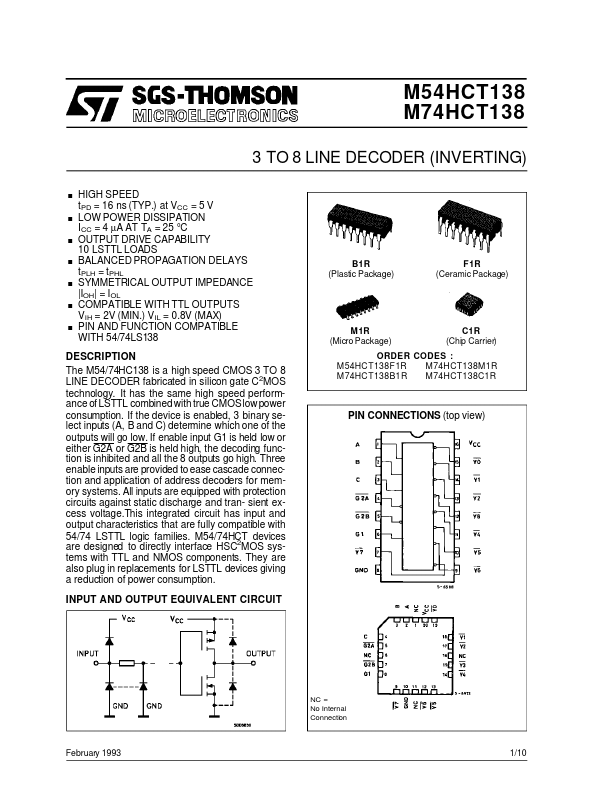

| Part | M74HCT138 |

|---|---|

| Description | 3 TO 8 LINE DECODER INVERTING |

| Manufacturer | STMicroelectronics |

| Size | 242.22 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 7404 | Fairchild Semiconductor | Hex Inverting Gates |

| XL6009 | XLSEMI | Boost / Buck-Boost / Inverting DC/DC Converter |

| XL6009E1 | XLSEMI | Boost / Buck-Boost / Inverting DC/DC Converter |