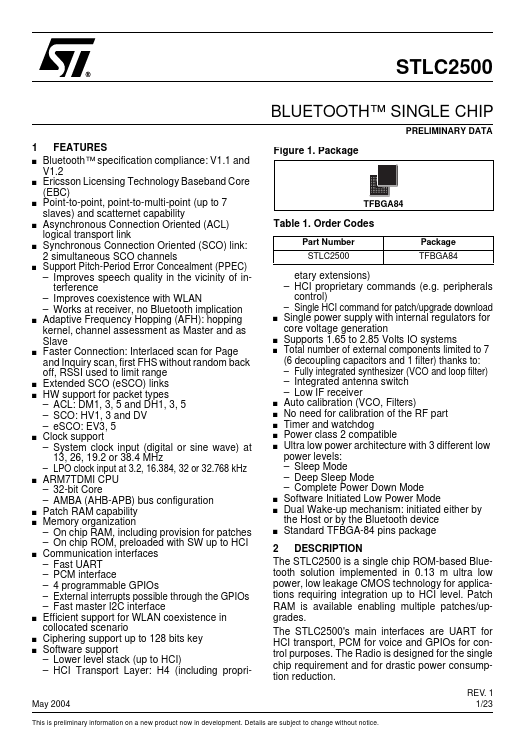

STLC2500

STLC2500 is BLUETOOTH SINGLE CHIP manufactured by STMicroelectronics.

BLUETOOTH™ SINGLE CHIP

PRELIMINARY DATA

- -

- -

- -

- -

- -

- -

- -

- -

- -

Features

Bluetooth™ specification pliance: V1.1 and V1.2 Ericsson Licensing Technology Baseband Core (EBC) Point-to-point, point-to-multi-point (up to 7 slaves) and scatternet capability Asynchronous Connection Oriented (ACL) logical transport link Synchronous Connection Oriented (SCO) link: 2 simultaneous SCO channels Support Pitch-Period Error Concealment (PPEC)

- Improves speech quality in the vicinity of interference

- Improves coexistence with WLAN

- Works at receiver, no Bluetooth implication Adaptive Frequency Hopping (AFH): hopping kernel, channel assessment as Master and as...