74112

Description

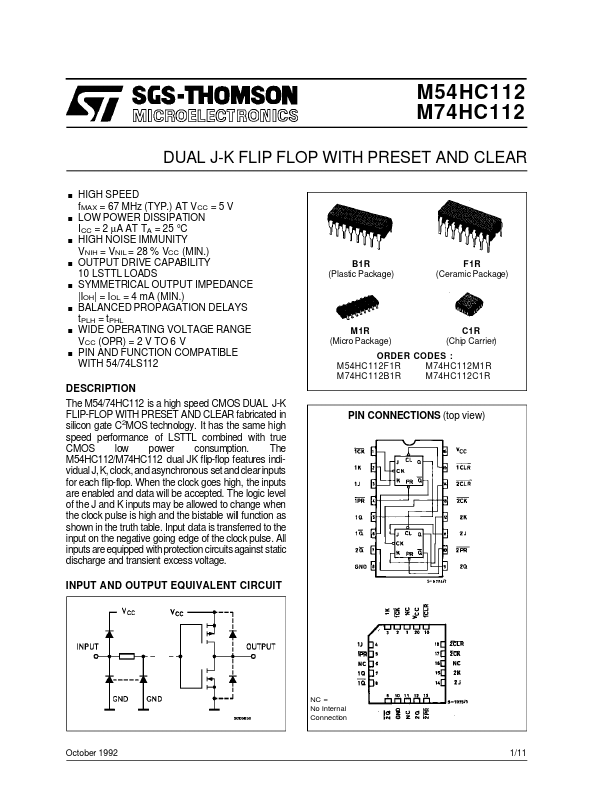

The M54/74HC112 is a high speed CMOS DUAL J-K FLIP-FLOP WITH PRESET AND CLEAR fabricated in silicon gate C2MOS technology.

Key Features

- individual J,K, clock, and asynchronous set and clearinputs for each flip-flop

- When the clock goes high, the inputs are enabled and data will be accepted

- Input data is transferred to the input on the negative going edge of the clock pulse

- All inputs are equipped withprotection circuits against static discharge and transient excess voltage