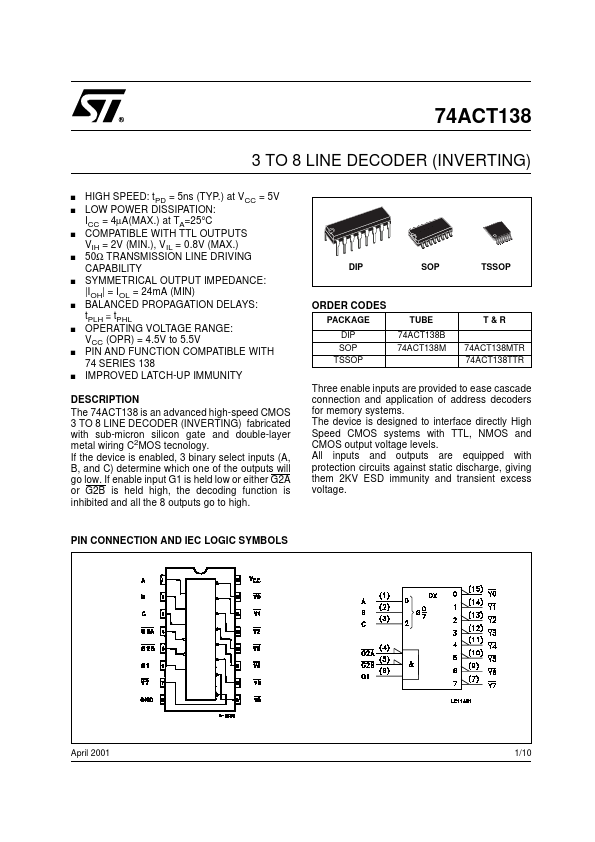

74ACT138

74ACT138 is 3 TO 8 LINE DECODER INVERTING manufactured by STMicroelectronics.

74ACT1284 IEEE 1284 Transceiver

June 1996 Revised November 1999

74ACT1284 IEEE 1284 Transceiver

General Description

The 74ACT1284 contains four non-inverting bidirectional buffers and three non-inverting buffers with open Drain outputs and high drive capability on the B Ports. It is intended to provide a standard signaling method for a bi-direction parallel peripheral in an Extended Capabilities Port mode (ECP). The HD (active HIGH) input pin enables the B Ports to switch from open Drain to a high drive totem pole output, capable of sourcing 14 mA on all seven buffers. The DIR input determines the direction of data flow on the bidirectional buffers. DIR (active HIGH) enables data flow...