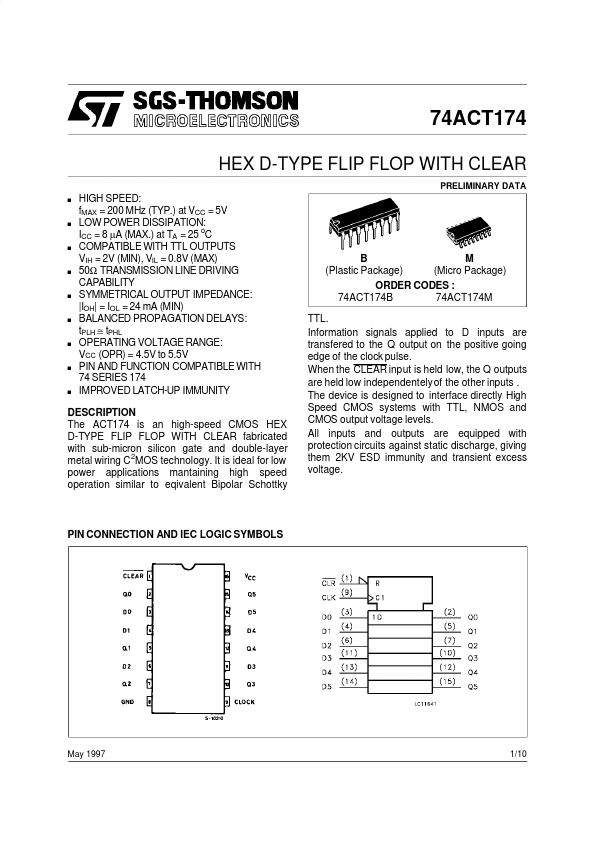

| Part | 74ACT174 |

|---|---|

| Description | HEX D-TYPE FLIP-FLOP |

| Manufacturer | STMicroelectronics |

| Size | 86.89 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74ACT175 | Fairchild Semiconductor | Quad D-Type Flip-Flop |

| 74ACT175 | Motorola Semiconductor | QUAD D FLIP-FLOP |