74LVQ174

74LVQ174 is HEX D-TYPE FLIP FLOP manufactured by STMicroelectronics.

®

HEX D-TYPE FLIP FLOP WITH CLEAR s s s s s s s s s s s

HIGH SPEED: fMAX = 150 MHz (TYP.) at VCC = 3.3V PATIBLE WITH TTL OUTPUTS LOW POWER DISSIPATION: ICC = 4 µA (MAX.) at TA = 25 oC LOW NOISE: VOLP = 0.3 V (TYP.) at VCC = 3.3V 75Ω TRANSMISSION LINE DRIVING CAPABILITY SYMMETRICAL OUTPUT IMPEDANCE: |IOH| = IOL = 12 mA (MIN) PCI BUS LEVELS GUARANTEED AT 24mA BALANCED PROPAGATION DELAYS: tPLH ≅ tPHL OPERATING VOLTAGE RANGE: VCC (OPR) = 2V to 3.6V (1.2V Data Retention) PIN AND FUNCTION PATIBLE WITH 74 SERIES 174 IMPROVED LATCH-UP IMMUNITY

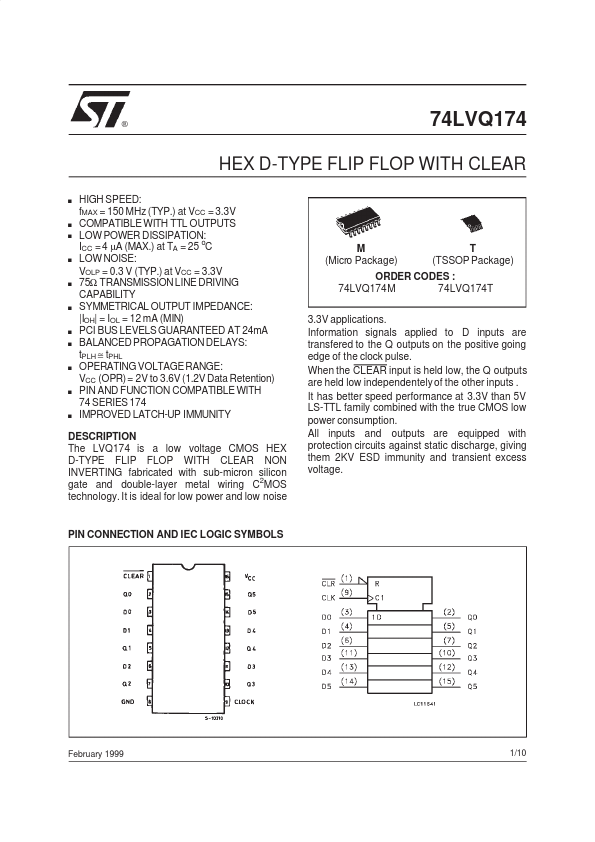

M (Micro Package)

T (TSSOP Package)

ORDER CODES : 74LVQ174M 74LVQ174T 3.3V applications. Information signals applied to D...