74V2G00

DESCRIPTION

The 74V2G00 is an advanced high-speed CMOS DUAL 2-INPUT NAND GATE fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. The internal circuit is posed of 3 stages including buffer output, which provide high noise immunity and stable output. Power down protection is provided on all inputs and outputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage. This device can be used to interface 5V to 3V.

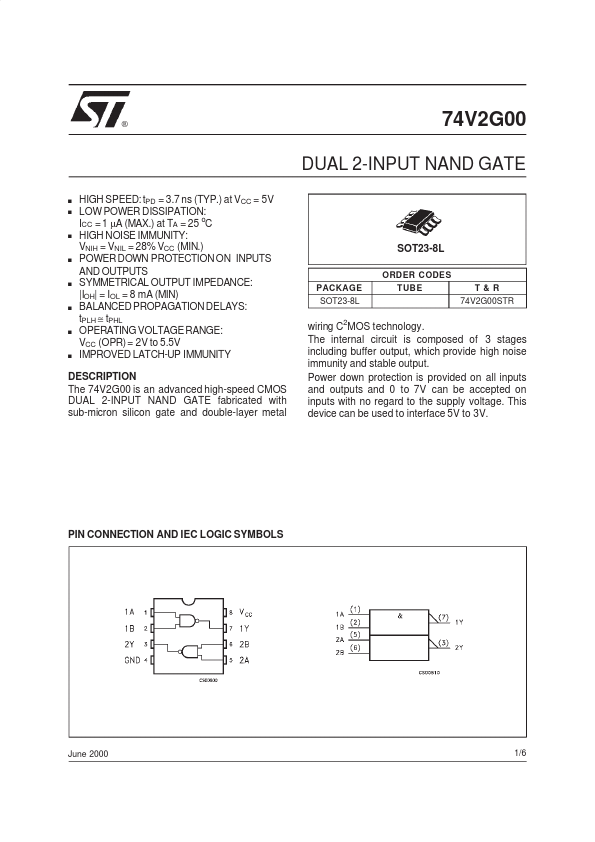

PIN CONNECTION AND IEC LOGIC SYMBOLS

June 2000

1/6

INPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

PIN No 1, 5 2, 6 7, 3 4 8 SYMBOL 1A, 2A 1B, 2B 1Y, 2Y GND VCC NAME AND FUNCT ION Data Input Data Input Data Output Ground (0V) Positive Supply Voltage

TRUTH TABLE

A L L H H B L H L H Y H H H L

ABSOLUTE MAXIMUM RATINGS

Symbol VCC VI VO VO IIK IOK IO Tstg TL Supply Voltage DC Input Voltage DC Output Voltage (see note 1) DC Output Voltage (see note 2) DC Input Diode Current DC Output Diode Current DC Output Current Storage...