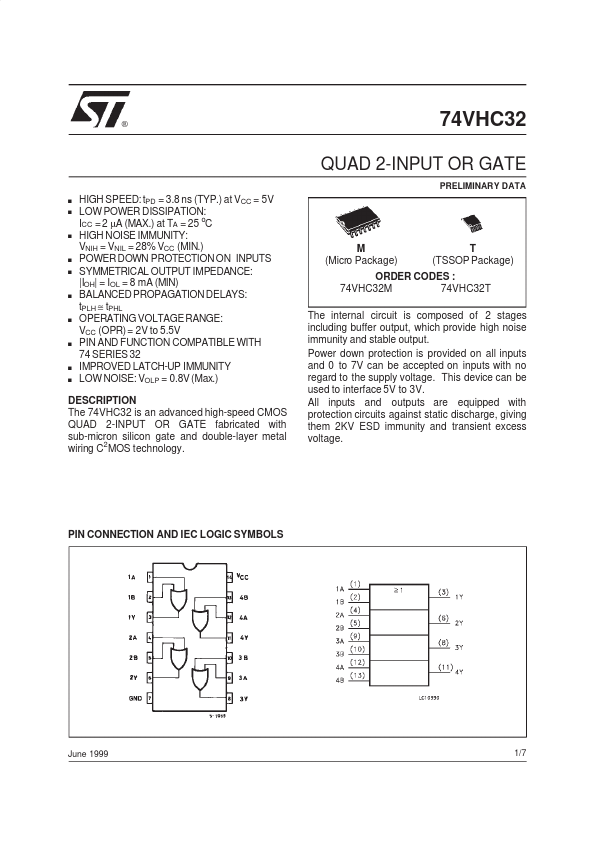

- Part: 74VHC32

- Description: QUAD 2-INPUT OR GATE

- Manufacturer: STMicroelectronics

- Size: 53.37 KB

Other 74VHC32 Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

| 74VHC32 | Quad 2-Input OR Gate | |

Motorola Semiconductor

Motorola Semiconductor |

74VHC32 | Quad 2-Input OR Gate |

| 74VHC32 | Quad 2-Input OR Gate | |

Nexperia

Nexperia |

74VHC32 | Quad 2-input OR gate |

Nexperia

Nexperia |

74VHC32-Q100 | Quad 2-input OR gate |