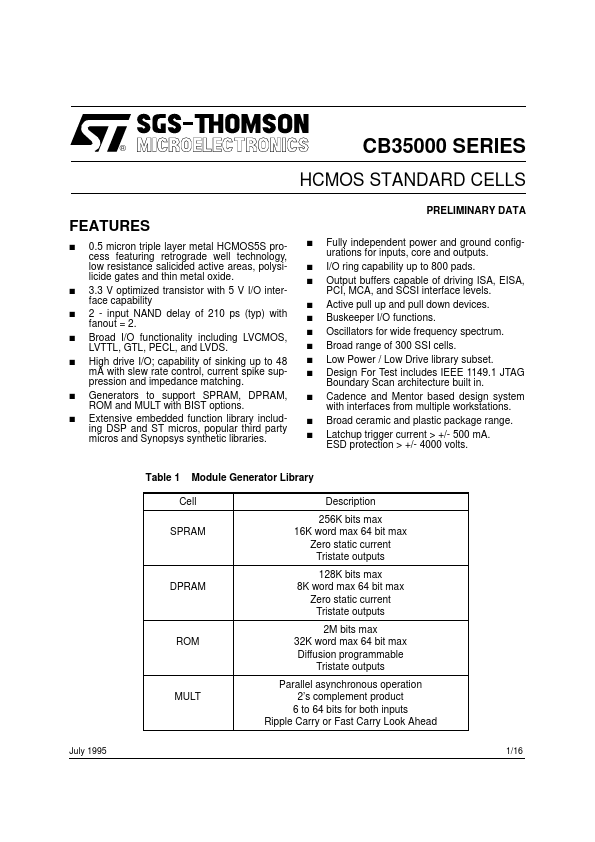

CB35000

FEATURES s s s s s s s

0.5 micron triple layer metal HCMOS5S process featuring retrograde well technology, low resistance salicided active areas, polysilicide gates and thin metal oxide. 3.3 V optimized transistor with 5 V I/O interface capability 2

- input NAND delay of 210 ps (typ) with fanout = 2. Broad I/O functionality including LVCMOS, LVTTL, GTL, PECL, and LVDS. High drive I/O; capability of sinking up to 48 m A with slew rate control, current spike suppression and impedance matching. Generators to support SPRAM, DPRAM, ROM and MULT with BIST options. Extensive embedded function library including DSP and ST micros, popular third party micros and Synopsys synthetic libraries. s s s s s s s s s s s s

Fully independent power and ground configurations for inputs, core and outputs. I/O ring capability up to 800 pads. Output buffers capable of driving ISA, EISA, PCI, MCA, and SCSI interface levels. Active pull up and pull down devices. Buskeeper I/O functions. Oscillators for wide...