HCC4096B

DESCRIPTION

OF B SERIES CMOS DEVICES” inputs is transferred to the Q and Q outputs on the positive edge of the clock pulse. SET and RESET inputs (active high) are provided for asynchronous operation.

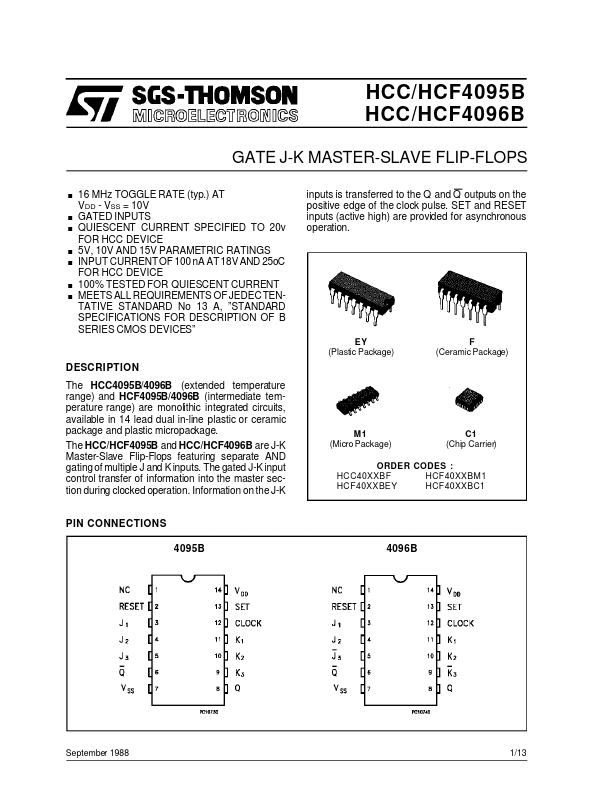

EY (Plastic Package)

F (Ceramic Package)

DESCRIPTION

The HCC4095B/4096B (extended temperature range) and HCF4095B/4096B (intermediate temperature range) are monolithic integrated circuits, available in 14 lead dual in-line plastic or ceramic package and plastic micropackage. The HCC/HCF4095B and HCC/HCF4096B are J-K Master-Slave Flip-Flops featuring separate AND gating of multiple J and K inputs. The gated J-K input control transfer of information into the master section during clocked operation. Information on the J-K PIN CONNECTIONS 4095B 4096B

M1 (Micro Package)

C1 (Chip Carrier)

ORDER CODES : HCC40XXBF HCF40XXBM1 HCF40XXBEY HCF40XXBC1

September 1988

1/13

HCC/HCF4095B HCC/HCF4096B

FUNCTIONAL DIAGRAMS

LOGIC DIAGRAM

TRUTH TABLES SYNCHRONOUS OPERATION (S=0 R=0)

Inputs Before...