M41ST87Y

M41ST87Y is 5.0 V and 3.3/3.0 V secure serial RTC and NVRAM supervisor manufactured by STMicroelectronics.

- Part of the M41ST87W comparator family.

- Part of the M41ST87W comparator family.

Features

- -

- -

- -

5.0, 3.3, or 3.0 V operation 400 k Hz I2C bus NVRAM supervisor to non-volatize external LPSRAM 2.5 to 5.5 V oscillator operating voltage Automatic switchover and deselect circuitry Choice of power-fail deselect voltages

- M41ST87Y: THS = 1: VPFD≈ 4.63 V; VCC = 4.75 to 5.5 V THS = 0: VPFD≈ 4.37 V; VCC = 4.5 to 5.5 V

- M41ST87W: THS = 1: VPFD ≈ 2.9 V; VCC = 3.0 to 3.6 V THS = 0: VPFD ≈ 2.63 V; VCC = 2.7 to 3.6 V Two independent power-fail parators (1.25 V reference) Counters for tenths/hundredths of seconds, seconds, minutes, hours, day, date, month, year, and century 128 bytes of clearable, general purpose NVRAM Programmable alarm and interrupt function (valid even during battery backup mode) Programmable watchdog timer Unique electronic serial number (8-byte) 32 k Hz frequency output available upon poweron Microprocessor power-on reset output Battery low flag Ultra-low battery supply current of 500 n A (typ)

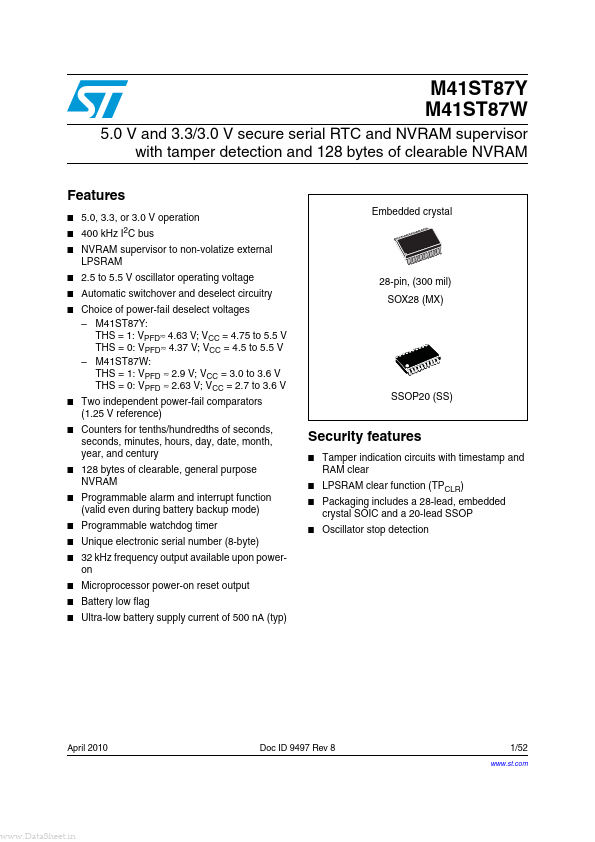

Embedded crystal

28-pin, (300 mil) SOX28 (MX)

- -

SSOP20 (SS)

Security features

- -

- -

- -

- -

- -

- -

Tamper indication circuits with timestamp and RAM clear LPSRAM clear function (TPCLR) Packaging includes a 28-lead, embedded crystal SOIC and a 20-lead SSOP Oscillator stop detection

April 2010

Doc ID 9497 Rev 8

1/52

.st. 1

.Data Sheet.in

Contents

M41ST87Y, M41ST87W

Contents

1 Description

- -

- -

- -

- -

- . . . . 6

1.1 Security features

- -

- -

- -

- - . . . . 6

Operating...