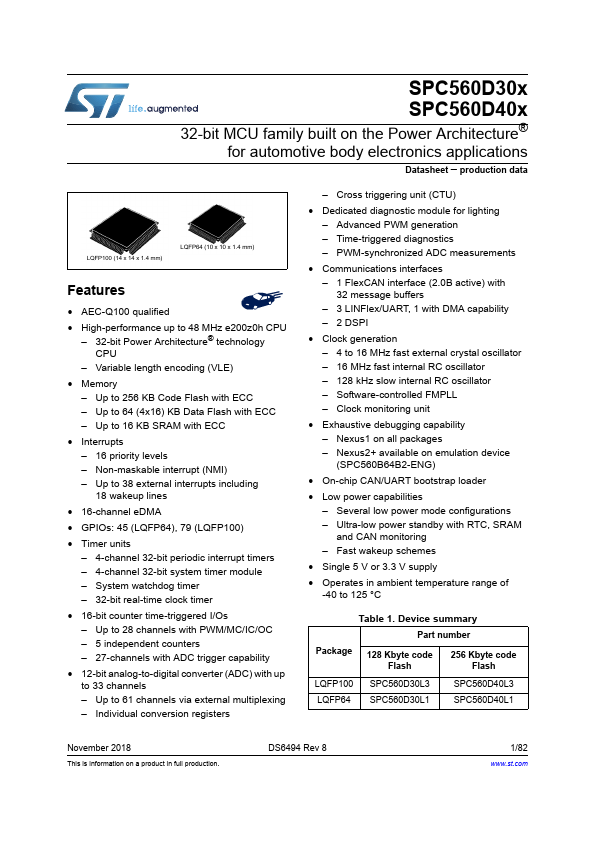

SPC560D40L1 Overview

Key Features

- AEC-Q100 qualified

- High-performance up to 48 MHz e200z0h CPU – 32-bit Power Architecture® technology CPU – Variable length encoding (VLE)

- Memory – Up to 256 KB Code Flash with ECC – Up to 64 (4x16) KB Data Flash with ECC – Up to 16 KB SRAM with ECC

- Interrupts – 16 priority levels – Non-maskable interrupt (NMI) – Up to 38 external interrupts including 18 wakeup lines

- 16-channel eDMA

- GPIOs: 45 (LQFP64), 79 (LQFP100)

- 16-bit counter time-triggered I/Os – Up to 28 channels with PWM/MC/IC/OC – 5 independent counters – 27-channels with ADC trigger capability

- Dedicated diagnostic module for lighting – Advanced PWM generation – Time-triggered diagnostics – PWM-synchronized ADC measurements

- Communications interfaces – 1 FlexCAN interface (2.0B active) with 32 message buffers – 3 LINFlex/UART, 1 with DMA capability – 2 DSPI

- Exhaustive debugging capability – Nexus1 on all packages – Nexus2+ available on emulation device (SPC560B64B2-ENG)